PORTD

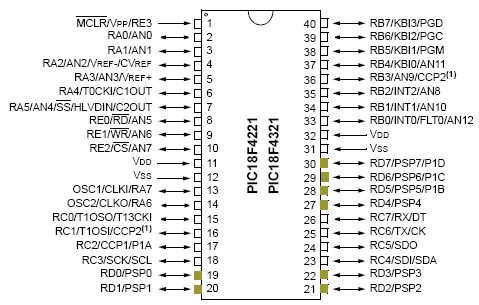

PORTD è un registro a 8 bit per uso generico (GPIO - General Purpose IO)

presente nei processori con package a più di 28 pin (nel nostro caso

PIC18F4321).

Ad esso è solitamente

associata la funzione di Parallel Slave Port (PSP) e, nei processori con

moduli CCP/PWM, alcune funzioni di questi.

In particolare PORTC supporta:

PSP

ECCP

Solitamente

PORTD è presente al completo con tutti gli 8 bit, da RD0 a RD7.

Fisicamente i pin si trovano qui:

|

Microchip mantiene un ragionevole senso nella disposizione delle

funzioni cercando di porle in modo successivo in corrispondenza dei

pin.

Però, tra package a 28 e 40 pin c'è forzatamente qualche differenza, anche

solo l' aumento dei pin di alimentazione da 3 a 4.

Però, data la disposizione dei pin, è possibile realizzare comunque dei

circuiti stampati o degli adattatori che possono portare entrambi i package

senza eccessiva difficoltà.

|

Nei chip a 28 pin PORT D

non è presente.

La tabella seguente riporta il quadro completo delle possibilità di PORT D.

|

Pin

|

Funzione

|

TRIS

|

I/O

|

Tipo

|

Descrizione

|

|

RD0

PSP0

|

RD0

|

0

|

O

|

DIG

|

LATD<0> uscita digitale

|

|

1

|

I

|

TTL

|

PORTD<0> ingresso digitale

|

| PSP0 |

- |

I |

DIG |

uscita dati PSP |

| - |

I |

TTL |

ingresso dati PSP |

RD1

PSP1 |

RD1 |

0 |

O |

DIG |

LATD<1>

uscita digitale

|

| 1 |

I |

TTL |

PORTD<1>

ingresso digitale

|

| PSP1 |

- |

O |

DIG |

uscita dati PSP

|

| - |

I |

TTL |

ingresso

dati PSP

|

RD2

PSP2 |

RD2 |

0 |

O |

DIG |

LATD<2>

uscita digitale

|

| 1 |

I |

TTL |

PORTD<2>

ingresso digitale

|

| PSP2 |

- |

O |

DIG |

uscita

dati PSP

|

| - |

I |

TTL

|

ingresso

dati PSP

|

RD3

PSP3

|

RD3 |

0 |

O |

DIG |

LATD<3>

uscita digitale

|

| 1 |

I |

TTL |

PORTD<3>

ingresso digitale

|

| PSP3 |

- |

O |

DIG |

uscita dati

PSP

|

| - |

I |

TTL

|

ingresso

dati PSP

|

RD4

PSP4 |

RD4 |

0 |

O |

DIG |

LATD<4>

uscita digitale

|

| 1 |

i |

TTL |

PORTD<4>

ingresso digitale

|

| PSP4 |

- |

O |

DIG |

uscita dati

PSP

|

| - |

I |

TTL

|

ingresso

dati PSP

|

RD5

PSP5

P1B |

RD5 |

0 |

O |

DIG |

LATD<5>

uscita digitale

|

| 1 |

I |

TTL

|

PORTD<5>

ingresso

digitale

|

| PSP5 |

- |

O |

DIG |

uscita dati PSP |

| - |

I |

TTL |

ingresso

dati PSP

|

| P1B |

0 |

O |

DIG

|

uscita

ECCP1 enhanced PWM canale B

|

RD6

PSP6

P1C |

RD6 |

0 |

O |

DIG |

LATD<6>

uscita digitale

|

| 1 |

I |

TTL |

PORTD<6>

uscita digitale |

| PSP6 |

- |

O |

DIG |

uscita dati PSP |

| - |

I |

TTL |

ingresso dati PSP |

| P1C |

0 |

O |

DIG |

uscita

ECCP1 enhanced PWM canale C

|

RD7

PSP7

P1D |

RD7 |

0 |

O |

DIG |

LATD<7>

uscita digitale

|

| 1 |

I |

TTL |

PORTD<7>

uscita digitale

|

| PSP7 |

- |

O |

DIG |

uscita dati PSP |

| - |

I |

TTL |

ingresso

dati PSP |

| P1D |

1 |

O |

DIG |

uscita

ECCP1 enhanced PWM canale D

|

- = non dipende dal registro TRIS

DIG = uscita digitale

TTL = buffer di ingresso livello logico

ST = ingresso con trigger di schmitt

ANA = ingresso (uscita) analogico

I pin di

PORT D

posso assumere le seguenti funzioni :

RISD. PORTD

è il registro dello stato della porta (in lettura e

scrittura), mentre LATD è il registro del latch della porta in uscita.

Parallel Slave Port (PSP)

La porta può essere dedicata (tutti i pin contemporaneamente) come

ingressi/uscite per una comunicazione parallela. I pin di controllo si

trovano in PORT E.

ingressi e uscite del modulo CCP

alcuni pin possono essere

dedicati come ingressi e/o uscite del modulo ECCP/CCP

Come solito, i pin dedicati ad una funzione non possono essere impiegati per

altre.

Nella tabella sono indicati lo stato del bit di TRISD

necessario alla funzione e il genere di ingresso/uscita.

Inizializzazione di PORTD

Anche per PORTD il default del POR fa assumere ai registri particolari

valori pre definiti e questo rende indispensabile, nelle prime fasi di inizializzazione

dell' hardware, dedicare una parte alla corretta definizione delle funzioni di

questi pin.

Il default per PORTD

è con tutti i bit configurati come ingressi digitali.

|

; Inizializza PORTD

clrf PORTD

; clear PORTD latch

movlw b'11001111'

; set RD7:6 e RD3:0 come input

movwf TRISD

; e RD5:4 come out

|

NOTE:

-

La funzione PSP è attivata settando il bit PSPMODE

(TRISE<4>) e

la direzione dei pin è indipendente dal PORTD

-

Le funzioni enhanced PWM sono disponibili solo su alcuni chip

Per quanto riguarda CCP, PWM e PSP consultare i capitoli relativi.

|

|

|

|

Copyright © afg. Tutti i diritti riservati.

Aggiornato il 09/12/10.

|