Microchip

raggruppa i PIC con bus dati a 8 bit in alcune famiglie, che si differenziano

per la loro struttura di base.

I più semplici appartengono al gruppo detto Baseline.

Possiamo raccogliere in una tabella le caratteristiche

principali della famiglia:

| |

Baseline |

| Pin |

6-40 |

| Livelli Interrupt |

nessuno |

| Performances |

5 MIPS |

| Core |

12 bit |

| Istruzioni

|

33 |

Memoria programma

(max)

|

3k |

| RAM (max) |

138 bytes |

| Livelli dello Stack |

2 |

Moduli Funzione

(non tutti disponibili

in tutti i modelli) |

- Timer0 8 bit

- comparatore

- ADC 8 bit

- oscillatore interno

|

| In evidenza |

Dimensioni ridotte

e costo limitato |

| Dispositivi in catalogo |

16 |

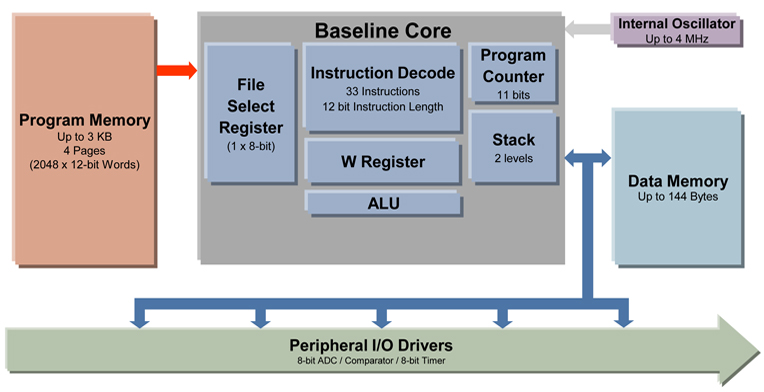

La struttura generale è rappresentabile con questo diagramma:

Baseline caratterizza chip semplifici al massimo: senza interrupt,

poche periferiche integrate, limitate risorse di memoria, anche in package

piccoli o piccolissimi (DFN, SOT23), con costi bassi e indirizzata all'

automatizzazione di processi in cui costo e dimensioni sono

determinanti.

Al momento attuale sono in produzione i seguenti chip:

| Product |

Program

Memory |

Self

write |

EEPROM

Memory |

RAM

|

I/O

Pins |

Fosc

max

MHz |

BOR |

Internal

Oscillator |

Comp. |

ADC |

#

of A/D Ch. |

Timers

8 bit |

ICSP |

Packages |

| PIC10F200 |

256 |

No |

- |

16 |

4 |

4 |

None |

4

MHz |

- |

- |

- |

1 |

Yes |

6/SOT-23 8/DFN 8/PDIP |

| PIC10F202 |

512 |

No |

- |

24 |

4 |

4 |

None |

4

MHz |

- |

- |

- |

1 |

Yes |

6/SOT-23 8/DFN 8/PDIP |

| PIC10F204 |

256 |

No |

- |

16 |

4 |

4 |

None |

4

MHz |

1 |

- |

- |

1 |

Yes |

6/SOT-23 8/DFN 8/PDIP |

| PIC10F206 |

512 |

No |

- |

24 |

4 |

4 |

None |

4

MHz |

1 |

- |

- |

1 |

Yes |

6/SOT-23 8/DFN 8/PDIP |

| PIC10F220 |

512 |

No |

- |

16 |

4 |

8 |

None |

4

MHz

8 MHz |

- |

1 |

2 |

1 |

Yes |

6/SOT-23 8/DFN 8/PDIP |

| PIC10F222 |

512 |

No |

- |

23 |

4 |

8 |

None |

4

MHz

8 MHz |

- |

1 |

2 |

1 |

Yes |

6/SOT-23 8/DFN 8/PDIP |

| PIC12F508 |

512 |

No |

- |

25 |

6 |

4 |

None |

4

MHz |

- |

- |

- |

1 |

Yes |

8/DFN 8/MSOP 8/PDIP 8/SOIC 150mil |

| PIC12F509 |

1k |

No |

- |

41 |

6 |

4 |

None |

4

MHz |

- |

- |

- |

1 |

Yes |

8/DFN 8/MSOP 8/PDIP 8/SOIC 150mil 8/SOIC

208mil |

|

PIC12F510 |

1k |

No |

- |

38 |

6 |

8 |

None |

4

MHz

8 MHz |

1 |

1 |

3 |

1 |

Yes |

8/DFN 8/MSOP 8/PDIP 8/SOIC 150mil |

|

PIC12F519 |

1k |

No |

64 |

41 |

6 |

8 |

None |

4

MHz

8 MHz |

-

|

-

|

- |

1 |

Yes |

8/DFN 8/MSOP 8/PDIP 8/SOIC 150mil |

|

PIC16F505 |

1k |

No |

- |

72 |

12 |

20 |

None |

4

MHz |

- |

- |

- |

1 |

Yes |

14/PDIP 14/SOIC 150mil 14/TSSOP 16/QFN |

| PIC16F506 |

1k |

No |

- |

67 |

12 |

20 |

None |

4

MHz

8 MHz |

2 |

1 |

3 |

1 |

Yes |

14/PDIP 14/SOIC 150mil 14/TSSOP 16/QFN

20/PDIP |

| PIC16F526 |

1k |

No |

64 |

67 |

12 |

20 |

None |

4

MHz

8 MHz |

2 |

1 |

3 |

1 |

Yes |

14/PDIP 14/SOIC 150mil 14/TSSOP 16/QFN |

| PIC16F527 |

1k |

Yes |

64 |

68 |

17 |

20 |

Yes |

4

MHz

8 MHz |

2 |

1 |

8 |

1 |

NO |

20/PDIP 20/QFN 20/SOIC 300mil 20/SSOP

208mil |

| PIC16F54 |

512 |

No |

- |

25 |

12 |

20 |

None |

- |

- |

- |

- |

1 |

Yes |

18/PDIP 18/SOIC 300mil 20/SSOP 208mil |

| PIC16F57 |

2k |

No |

- |

72 |

20 |

20 |

None |

- |

- |

- |

- |

1 |

Yes |

28/PDIP 28/SOIC 300mil 28/SPDIP 28/SSOP

208mil |

| PIC16F570 |

2k |

Yes |

132 |

64 |

24 |

20 |

Yes |

8

MHz |

2 |

1 |

8 |

1 |

NO |

-

|

| PIC16F59 |

2k |

No |

- |

134 |

32 |

20 |

None |

- |

- |

- |

- |

1 |

Yes |

40/PDIP

600mil 44/TQFP |

| PIC16F707 |

8k |

No |

- |

368 |

36 |

20 |

Yes |

16

MHz |

- |

1 |

14 |

3 |

Yes |

40/PDIP 40/UQFN 44/QFN 44/TQFP |

La situazione aggiornata alla data di oggi la trovate con la ricerca

parametrica sul sito di Microchip.

Si può notare che questi chip sono prevalentemente in packages piccoli (6-14 pin),

con oscillatore interno, per ridurre il numero di componenti esterni e con

un set di periferiche molto limitato, per ridurre il costo.

Si possono raccogliere in alcuni sottogruppi, analoghi per

caratteristiche:

- 10F200/202 e 10F202/204

- 10F220/222

- 12F508/509/16F505

- 12F510/16F506

- 16F5x

In genere, le differenze consistono in una diversa disponibilità di

memoria o di I/O. Ad esempio, 10F202 dispone del doppio di memoria programma

di 10F200. Questo vuol dire che il sorgente scritto per il secondo potrà

essere passato al primo con la sola modifica della definizione del

processore e che l' opposto sarà possibile restando nei limiti del minore.

La situazione è molto interessante in quanto si potrà scrivere un

programma per un micro della famiglia con la certezza di poterlo portare su

un' altro chip con un numero di modifiche limitate. Ovviamente in questo

passaggio non si potranno utilizzare periferiche disponibili solo su un tipo

di chip: ad esempio, il software scritto per 10F200 potrà essere passato

con la sola modifica del tipo di processore al 10F204; sarà possibile l'

inverso solo se il programma non utilizza la funzione comparatore che è

presente nel secondo, ma non nel primo.

La semplicità ha comunque le sue contropartite.

La mancanza di una gestione ad interrupt può limitare alcune applicazioni,

dato che costringe a realizzare algoritmi che analizzano i flag via polling,

mentre la struttura generale prevede che si generino reset, con la

possibilità di discriminarne la causa.

L' utilizzo di questi microcontroller nel campo dell' istruzione è

adeguato, in quanto in gran parte non hanno le complicazioni presenti nei

Mid-range, hanno un set di istruzioni semplice da memorizzare e, nonostante

le piccole dimensioni della memoria e dello stack, possono anche essere

approcciati con un compilatore C.

Per contro risentono dello stcak a due soli livelli, che limita

drasticamente l' annidamento delle chiamate.

Un altro elemento problematico può essere dato della mancanza di un motore

di debug interno (ICD), che è dovuta al basso numero di pin disponibili.

Questo impedisce il debug-in-circuit realizzato con tools economici come il

Pickit e che consente l' avanzamento passo-passo, i breakpoint, l'analisi

dei registri, ecc..

Di ogni chip esistono comunque le versioni -ICD che vengono fornite in sub

moduli (headers) per avere la possibilità di debug diretto.