Una introduzione ai

Microcontroller PIC

|

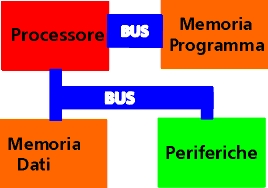

I BUS

Non "un bus", ma più bus nei PIC !

|

Come abbiamo visto, l' architettura Harvard prevede bus separati per

l' accesso alla memoria dati e quella delle istruzioni.

Essendo separati, i due bus possono avere ampiezze diverse: ad

esempio, nei PIC con bus dati a 8 bit, il bus istruzioni può essere

ampio 12, 14 o 16 bit.

Il che vuol, dire che avremo disponibili PIC a 8 bit dati con codici

di istruzione implementati su 12/14 o 16 bit. |

Possiamo allora distinguere i PIC a 8 bit dati a seconda dell'

ampiezza del bus istruzioni:

-

bus istruzioni a 12 bit: Base-Line. PIC10F, 1xF5x e

alcuni 16F

-

bus istruzioni a 14 bit: Mid-Range. PIC12F, 16F

-

bus istruzioni a 16 bit: Enhanced. PIC18F

Troveremo poi PIC 16 e 32 bit: PIC24/30/33/dsPIC.

Va compreso che l' ampiezza in bit delle istruzioni non ha niente a che

fare con quella dei dati.

Infatti, nella struttura RISC, un codice di istruzione sarà più ampio

di quello di un dato in quanto conterrà non solo il codice dell'

istruzione in se, ma anche l' indirizzo di destinazione o il dato su ci

lavorare.

In particolare, l' indicazione data dal costruttore a riguardo del

Core identifica non l' ampiezza dei dati, ma quella della

codifica delle istruzioni. |

Vediamo di chiarire ulteriormente questo punto.

Nei PIC, abbiamo una famiglia con bus dati a 8 bit.

Cosa comporta questo ?

Ricordiamo che nell' architettura Harvard il bus dei dati è

comune alla memoria dati, ai registri di controllo e alle periferiche di I/O.

|

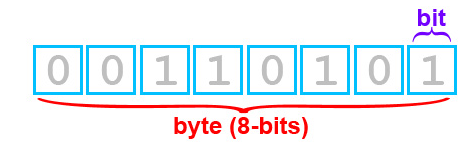

Questo vuol dire che ognuno di questi elementi è composto

da 8 bit,

ovvero da un byte.

Occorreranno fisicamente 8 conduttori per costituire questo

bus e trasportare i segnali elettrici dall' unità centrale alle

periferiche e alla memoria dati. |

Abbiamo però, nella stessa grande famiglia dei processori a 8

bit, tre sotto famiglie che si differenziano per l' ampiezza del bus che

collega l' unità centrale alla memoria programma.

Abbiamo così controller con bus istruzioni a :

Per cui sarà diversa la quantità di conduttori che collegano

l' unità centrale e le memoria programma, pur restando inalterata l'

ampiezza di 8 conduttori per il collegamento con le periferiche e la memoria

dati.

A che pro questa soluzione apparentemente bizzarra?

Abbiamo detto che l' istruzione RISC contiene nel suo codice sia l' istruzione

vera e propria, sia l' indirizzo o il dato con cui operare.

Questo permette in generale che una istruzione sia elaborata in un solo ciclo

(anche se alcune istruzioni ne richiedono due).

L' utilizzo di un solo ciclo per istruzione consente di migliorare le

prestazioni in MIPS.

Dovrebbe essere evidente che una maggior

ampiezza del codice istruzioni, ovvero più bit disponibili, consente di avere:

-

la possibilità di codificare un maggior numero di

istruzioni

-

la possibilità di indirizzare un più ampio spazio di

memoria

-

la possibilità di trattare dati di maggiore ampiezza

Ne consegue che:_

-

i processori con core a 12 bit hanno set di

istruzioni limitati, segmentazione in pagine della memoria programma e in

banchi della memoria dati e dei registri delle periferiche.

-

I PIC con core a 14 bit avranno la possibilità di implementare più codici di

istruzione

-

quelli a 16 bit potranno avere un set ancora più ampio e gestire

aree di memoria più grandi, evitando, ad esempio, la paginazione della memoria

programma.

Bisogna evitare un' altra possibile confusione.

Con un bus dati a 8 bit, una dato a 16 bit richiederà due registri

di memoria, un dato a 24 bit ne richiederà 3 e così via.

Dato che il bus può trasportare solo 8 bit di dati per volta,

occorreranno più operazioni per trasferire quantità di dati più

ampie di 8 bit.

Questo vuol anche dire che le locazioni di memoria RAM o EEPROM e i

regsitri di controllo (SFR) delle funzioni e delle periferiche sono

tutti ampi 8 bit.

E il registro di lavoro WREG, o, in altri termini l'

accumulatore, è pure a 8 bit.

In un processore con bus dati a 16 bit potranno essere trattati

dati di ampiezza doppia di quelli dei processori a 8 bit; e così via.

Nel bus istruzioni il problema è differente: nei processori

a 8 bit dati le istruzioni base

sono ampie 12, 14 o 16 bit.

Si potrebbe parlare di "byte" impropri, costituiti da 12 o

14 bit, mentre si preferisce usare genericamente la parola word,

che ufficialmente indica l' ampiezza di 16 bit (16 bit = 2 bytes = 1 word).

Le celle di memoria programma sono

ampie 12 o 14 e TUTTI questi bit dispongono di un

proprio conduttore di trasmissione e sono spostati tutti

contemporaneamente.

Negli Enhanced, dove l' istruzione tipica è a 16 bit, le celle

della memoria programma sono a 8 bit. Questa scelta è dovuta al fatto

che è possibile accedere in lettura e scrittura alla memoria flash

attraverso il programma stesso, con le istrusioni del set esteso e il

registro TABLAT, che, essendo un SFR, è a 8 bit.

Quindi il programma viene posizionato in memoria a coppie di byte e

ogni coppia costituisce una istruzione, o opcode, e tutti e 16 i bit

si muoveranno contemporaneamente all' esecuzione del fetch dell'

istruzione.

Che impiega comunque 1 ciclo per l' esecuzione.

Nel caso in cui si abbia a che fare con istruzioni a più

"word", solo allora l' unità centrale dovrà effettuare

più operazioni per il prelievo dell' istruzione dalla memoria

programma, impiegando due cicli. |

Va anche notato che la prima istruzione che verrà eseguita si

trova all' indirizzo del Vettore di Reset, che per i PIC è 0000h.

Ne deriva che gli opcodes dei PIC Base e Mid, dove l'

istruzione tipica è lunga 1 byte (occupa una cella da 12 o 14 bit in flash),

si possono trovare a indirizzi sia pari che dispari.

Nei PIC18, invece, le istruzioni ampie 16 bit occupano DUE

celle in flash (da 8 bit ciascuna), per cui si possono trovare esclusivamente

ad indirizzi pari. Di conseguenza il bit 0 del Program Counter sarà sempre a

0, a meno che venga modificato manualmente.

E l' assegnazione di una origine dispari, ad esempio:

nei PIC18F è vietata e origina un errore in compilazione.

Dal punto di vista dell' esecuzione del programma, gli

automatismi del program counter rendono questa struttura trasparente per l'

utente, a meno che non si eseguano operazioni che vadano a toccare manualmente

il program counter stesso,

dove viene richiesta una serie di attenzioni particolari.

Proviamo a raccogliere in una tabella i dati di

massima relativi ai PIC con bus dati a 8 bit:

Core

|

Core a 12

bit

|

Core a 14

bit

|

Core a 16

bit

|

| Famiglia |

Base-Line |

Mid-Range |

Enhanced |

| Istruzione a |

12 bit |

14 bit |

16 bit |

| Memoria programma |

256 .. 2k

a 12 bit per cella |

1 .. 8k

a 14 bit per cella |

4k .. 128k

a 8 bit per cella |

| Paginazione |

no |

si |

no |

| EEPROM [byte] |

0 |

0 .. 256 |

0 .. 1024 |

| RAM [byte] |

16 .. 134 |

64 .. 368 |

256 .. 3936 |

| Livelli Stack |

2 |

8 |

31 |

| Ampiezza PC e stack |

13 bit |

13 bit |

21 bit |

| Interrupt |

no |

si |

con priorità |

| Package |

6-40 pin |

8-40 pin |

18-100 pin |

| Clock [MHz] |

4-20 |

4-20 |

4-40 e oltre |

| Set istruzioni |

33 |

35 |

75 |

| Componente tipico |

10F200

16F505

16F59 |

16F84

16F876

12F675 |

18F242

18F2321

18F4580 |

| Caratteristiche |

Piccoli, poco costosi.

Set di istruzioni limitato.

Senza interrupt e con stack a due soli livelli.

Adatti per applicazioni Assembly. |

Economici e molto diffusi.

Memoria paginata.

Per uso generale. |

Top della gamma a 8 bit.

Set di istruzioni esteso, nessuna paginazione in memoria.

Ampio set di periferiche.

Ottimizzati per l' impiego con il C. |

La tabella è puramente indicativa, in quanto la produzione di Microchip è

continua e ogni anno sono aggiunti nuovi modelli con caratteristiche diverse e

superiori, ad esempio nella famiglia 16F, dove si stanno introducendo alcune

caratteristiche degli Enhanced.

Una completa informazione sui vari prodotti è facilmente consultabile al sito

del produttore.

Limitandoci per ora all' analisi dei PIC con dati a 8 bit, dalla tabella

qui sopra possiamo evidenziare alcuni punti importanti:

- la disponibilità di memoria programma aumenta con la complessità

del chip. Questo è evidentemente corretto, in quanto maggiori saranno

le possibilità e prestazioni, maggiore sarà la probabilità che il chip

venga usato in applicazioni altrettanto complesse e richieda quindi

programmi ampi. In particolare, i linguaggi evoluti richiedono normalmente

una massa di memoria programma molto ampia; di conseguenza i piccoli PIC

si presteranno meno all' uso di C e BASIC, comunque sempre possibile.

| Va notato che la disponibilità è reale in rapporto alle

istruzioni (sempre fatte salve quelle a lunghezza doppia) per

i Base e Mid.

Ma è la metà per gli Enhanced, che usano 2 bytes per

istruzione (sempre fatte salve quelle a lunghezza doppia).

Ne deriva che Microchip, per correttezza, fornisce sia un dato

in bytes, sia uno dimezzato in words per l' ampiezza della memoria

flash dei PIC18F. |

- la disponibilità di memoria RAM ha un andamento analogo, per le

stesse ragioni

- l' integrazione di EEPROM nel chip richiede un costo aggiuntivo,

per cui nei dispositivi Base-Line, che puntano ad applicazioni a costo

ridotto, questa parte non è implementata

- il discorso della complessità dei programmi vale anche per le

dimensioni dello stack. Uno stack ridotto, a due soli livelli, non

permetterà una ricorsività se non minima. Inoltre, sempre i linguaggi ad

alto livello, fortemente ricorsivi, troveranno ampio beneficio in una

struttura di stack evoluta come quella della famiglia Enhanced

- l' interrupt, funzione chiave del microcontroller, è assente dai

Base-Line, per la ragione già detta del target di questi chip, mentre

negli Enhanced si aggiunge la possibilità di applicare non un vero e

proprio DMA, riservato a processori di classe superiore, ma almeno una

priorità a due livelli.

- la dimensione del package fa riferimento essenzialmente al numero

di I/O disponibili ed arriva fino ai 100 pin dei packages SMD della

famiglia Enhanced.

- la frequenza del clock, in un range tra 4 e 20 MHz per i PIC Base

e Mid, cresce a 40 MHz e oltre nei PIC superiori. Tenendo presente che la

struttura RISC consente di eseguire la maggior parte delle istruzioni in

un solo ciclo (pari ad 1/4 del periodo del clcok) ci si rende conto delle

levate possibilità di elaborazione di componenti così piccoli

- per ultimo, il set di istruzioni si amplia con l' ampliarsi della

dimensione in bit dell' istruzione stessa. Inoltre, il maggior spazio

consente agli Enhanced l' indirizzamento diretto di 2 GB di memoria

programma, eliminando la scomoda paginazione presente nei Mid-Range

Va tenuto ben presente, però, che la disponibilità di maggiori risorse o

prestazioni non è un fattore chiave in ogni scelta, nel senso che sarà

insensato utilizzare un processore con 100 pin in una applicazione che

interessa due I/O, non serviranno 2GB di memoria per un piccolo programma in

Assembly e neppure frequenze di 48 MHz dell' oscillatore primario per

realizzare un Real Time Clock.

Ovvero, saranno le specifiche dell' applicazione a determinare quale è

il chip più adatto.

Diversa sarà invece la valutazione da fare nel caso di istruzione o

sperimentazione: come già detto, in questi casi è molto interessante

avere a disposizione il maggior numero di possibilità.

Argomenti collegati:

|