Una introduzione ai

Microcontroller PIC

|

Architettura Harvard - RISC

I PIC sono definibili come processori RISC ad architettura

Harvard.

|

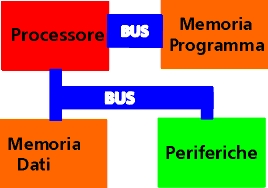

L'architettura è di tipo Harvard dispone di bus separati per dati e

periferiche e un' altro per le istruzioni.

Quindi, la gestione della memoria dati e delle istruzioni avviene su

circuiti separati. L' unità centrale può effettuare un accesso ai due

bus contemporaneamente e, sfruttando sistemi di pipeline, si può

eseguire una istruzione per ogni ciclo macchina.

I due bus possono avere ampiezze diverse: ad esempio, nei PIC con bus

dati a 8 bit, il bus istruzioni può essere ampio 12, 14 o 16 bit.

Questa struttura si presenta come la più adeguata a macchine RISC. |

Da osservare che non c'è niente di strano, quindi, nel fatto

che in uno stesso processore si abbia, ad esempio:

- il bus dati da 8 bit

- la larghezza del bus istruzioni di 14 bit

E di conseguenza:

- le locazioni di memoria programma siano ampie ciascuna 14 bit

- quelle della memoria RAM e degli SFR siano da 8 bit

pur facendo sempre riferimento, anche se impropriamente, a "bytes"

e "words".

Ed è altrettanto normale che questi pacchetti di bit siano trattati

dal processore in una unica azione, indipendentemente dalla loro

ampiezza, dato che istruzioni e dati si muovono su bus separati,

trattati da diverse parti dell' ALU.

|

Un sistema RISC è tale quando implementa un numero limitato di

codici di istruzione (opcodes), basilari ed eseguibili in un solo ciclo di cloc.

Per ottenere funzioni più complesse si assembleranno queste istruzioni

elementari in opportuni algoritmi.

E' importante notare che la struttura

di una istruzione di questo genere contiene, oltre al significato dell' istruzione stessa,

anche l'indirizzo di memorizzazione o di salto o il dato su cui operare.

In queste condizioni,

onde non far crescere l'ampiezza del bus istruzioni (costo e complessità), la

memoria viene segmentata in pagine e banchi.

Per cambiare segmento o banco

in uso occorre agire su appositi registri, fatto che complica la programmazione

dei PIC nell' uso di linguaggio Assembly.

Questo problema è meno sentito nel caso di impiego di linguaggi di alto livello,

che possono integrare meccanismi automatici di gestione delle pagine e dei

banchi, oppure di Macro Assembler che permettono di implementare meccanismi

analoghi.

Questo problema pagine/banchi è presente nei PIC delle famigli

Base-line e Mid-range, mentre è attenuato o meno rilevante in quelle successive.

E questa è una ragione per può essere consigliabile iniziare la sperimentazione

in Assembly sui

PIC partendo dai PIC18F e non dai PIC16F.

Consideriamo adesso la struttura interna delle periferiche di un PIC tipo.

|