Modo Slave

Il modulo MSSP permette anche alcune configurazioni come Slave.

I2C consente di gestire

sistemi multi-Master e un Master, abbiamo visto, può trasmettere e ricevere

dati da un' altra periferica. E un Master può, in certo momento, essere

Slave di un' altro Master.

Il protocollo I2C definisce la differenza sostanziale tra Master

e Salve

- il dispositivo Master può avviare un a comunicazione sul bus

- il dispositivo Slave non può iniziare una comunicazione e può solamente

rispondere alle richieste del Master

In tal senso è possibile che si richieda al microcontroller di eseguire una

funzione di Slave "intelligente" al servizio di altri Master sul bus.

Attraverso SSPCON2 è possibile programmare il PIC per le seguenti modalità:

- Slave con indirizzo a 7 bit

- Slave con indirizzo a 10 bit

- Slave con indirizzo a 7 bit e interrupt per le condizioni di Start e

Stop abilitato

- Slave con indirizzo a 10 bit e interrupt per le condizioni di Start e

Stop abilitato

Da Master a Slave

In un sistema multi-Master,

quindi, potrebbe esse richiesto ad un Master di

poter rispondere come Slave alla chiamata di un altro Master.

Questa situazione va ben distinta da quella di Master

ricevente/trasmittente: qui abbiamo un Master che invia sul bus l'

indirizzo attribuito ad una periferica che è un Master, ma in questo

caso dovrà operare come Slave.

Le differenze sono notevoli:

- il Master genera il clock sul bus quando riceve e quando

trasmette. Lo Slave non genera alcun clock

- il Master non ha indirizzo, lo Slave si.

Se un microcontroller deve eseguire questa funzione, il software dovrà

commutare il setup dell' MSSP da modo Master a modo Slave e

re-inizializzarlo.

Il modulo va spento durante queste operazioni, che possono essere fatte in

qualsiasi momento e in entrambe le direzioni.

Quindi, per un microcontroller dotato di modulo MSSP, la funzione di

Master

o Slave potrà dipendere dal programma di gestione e potrà essere variata a

seconda delle circostanze.

Modo Slave con interrupt per Start e Stop abilitati

Sono programmabili due modalità di Slave con indirizzo a 10 bit e

due con indirizzo a 7 bit, attraverso i bit SSMP di SSPCON2.

SSPM3:0

: Mode select

1111 =

I2C Slave con indirizzo a 10 bit con interrupt per Start e Stop

1110 =

I2C Slave con indirizzo a 7 bit con interrupt per Start e Stop

0111 =

I2C Slave con indirizzo a 10 bit

0110 =

I2C Slave con indirizzo a 7 bit

La differenza consiste nel fatto che, negli ultimi due modi, l' interrupt

è generato dal completamento del byte in ricezione e trasmissione, ovvero,

essenzialmente, dalle condizioni di SSPBUF.

Nei primi due modi è generato un interrupt anche per il rilevamento

delle condizioni Start e Stop, distinguibili con i flag S e P.

Questo consente di avere un maggiore controllo sulle condizioni di Start e

Stop del bus.

Per il resto le modalità sono analoghe.

Configurazione del modo Slave

Per prima cosa occorre tenere presente che

in modo Slave SCL e SDA devono essere inizialmente configurati come input

(TRISC<4:3>=1).

Il modulo MSSP modificherà la direzione quando necessario. |

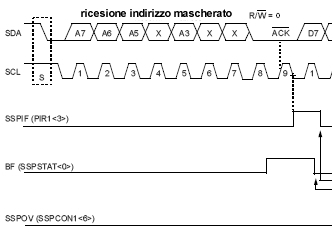

L' utente deve assegnare al microcontroller un indirizzo. In qualsiasi delle configurazioni Slave possibili, il modulo MSSP

genererà un interrup al momento del riconoscimento del suo indirizzo.

La mascheratura dell' indirizzo permetterà all'hardware di generare un interrupt per più di un indirizzo (fino a 31 in modalità di indirizzamento

7 bit e fino a 63 in modalità di indirizzamento 10 bit).

Attraverso i bit di selezionare

della modalità l'utente può scegliere anche l' interrupt per il rilevamento

della condizione di Start e Stop.

Quando quando l' indirizzo è verificato o è ricevuto il dato dopo un match di indirizzo, l'hardware automaticamente genererà l'impulso di

riconoscimento (ACK) e caricherà il registro SSPBUF con il valore ricevuto al

momento presente nel SSPSR. Qualsiasi combinazione delle seguenti condizioni

non permetterà al modulo MSSP di dare l' ACK:

- Il bit di buffer full, BF (SSPSTAT <0>), è stato impostato prima che il

dato sia ricevuto.

- Il bit di overflow, SSPOV (SSPCON1<6>), è stato impostato prima che il

dato sia ricevuto.

In questo secondo caso, il valore di registro SSPSR non viene caricato nel

SSPBUF, ma bit SSPIF (PIR1<3>) è

settato. In questo modo il programma di gestione è avvisato dell' evento

ei flag BF e/o SSPOV indicheranno la causa dell' anomalia.

-

Il bit BF è cancellato dalla lettura del Registro SSPBUF

Il

bit SSPOV è da cancellare

via software.

|

L'input di clock SCL deve avere i giusti parametri per il corretto

funzionamento; i tempi della specifica I2C, come pure gli altri requisiti dei

segnali relativi al modulo MSSP, sono indicati nel parametro di temporizzazione 100 e 101.

Configurazione dello Slave.

Prima di poter utilizzare il modulo MSSP come Slave, occorre configurarlo.

Supponiamo di voler impostare il PIC per un funzionamento:

- in modo Slave standard

- all' indirizzo 0x26 (7 bit)

- con accettazione della General Call

occorreranno i seguenti passi:

- Programmiamo il registro TRISC (direzione del PORTC) come ingressi per i pin

SCL (RC3) e SDA (RC4).

- Selezioniamo con i bit SSMP di SSPCON1 la modalità Slave

- Configuriamo SSPSTAT portando a 0 il bit SMP per la compatibilità con I2C

- impostiamo l' indirizzo in SSPADD con il bit 0=0, ricordando che occupa

i bit 7:1

- Accendiamo il modulo con il bit SSPEN di SSPCON1

In Assembly:

|

; Configura MSSP per Slave

I2C all' indirizzo 0x26

i2c_setssp bsf

TRISC,3 ;

SCL input

bsf TRISC,4

;

SDA input

movlw b'00001110'

; modo

Slave a 7 bit

movwf SSPCON1

movlw b'10000000'

;

abilita

General Call

movwf SSPCON1

movlw (Address * 2)

; indirizzo shiftato a sinistra

movwf SSPADD

bsf

SSPCON1,SSPEN ;

accendi MSSP

|

Analogamente per lo Slave a 10 bit; si tratterà però di caricare in

SSPADD il primo byte dell' indirizzo.

Indirizzamento dello Slave

Una volta che è stato attivato il modulo MSSP, esso resta in

attesa di verificare sul bus una condizione di Start.

A seguito di questa, gli 8 bit inviati dal Master vengono spostati nel

registro SSPSR, campionandoli sul fronte di salita del clock (SCL) inviato

dal Master.

Il valore del registro SSPSR<7:1> è comparato al valore

del registro SSPADD<7:1> sul fronte di discesa dell'ottavo impulso

di clock.

Se i valori sono uguali e i flag BF e SSPOV sono a zero, si verificano i

seguenti eventi:

- il contenuto del registro SSPSR viene caricato in SSPBUF

- Il flag di Buffer Full, BF, va a 1.

- Viene generato automaticamente una condizione di ACK.

- Il flag di interrupt, SSPIF (PIR1 <3>), è settato e, se

abilitato, viene generato un interrupt sul fronte di discesa del nono

impulso di clock.

In modalità a 7 bit il byte di indirizzo vale:

| bit |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| valore |

A7 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

0 |

| note |

indirizzo |

R/W |

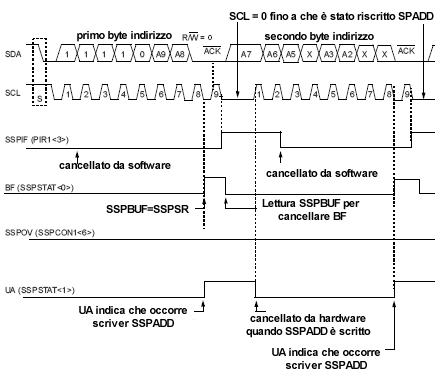

Più laboriosa è la sequenza di avvio per indirizzi a 10 bit, dato che

occorre recuperare due byte per completare l' indirizzo.

I cinque bit più significativo (MSbs) del primo byte indirizzo

specificano se si tratta di un indirizzo a 10 bit ed hanno il valore fisso

"11110".

Il bit di R/W (SSPSTAT<2>) deve

essere a zero per indicare una scrittura in modo tale che lo Slave riceva il

secondo byte dell'indirizzo.

Per un indirizzo a 10-bit, quindi, il primo byte sarà uguale '11110 A9 A8 0 ', dove' A9 'e' A8 'sono i due MSB del

indirizzo.

| bit |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| valore |

1 |

1 |

1 |

1 |

0 |

A9 |

A8 |

0 |

| note |

indicatore |

MSb |

R/W |

dove 'A9' e 'A8' sono i due MSb dell'indirizzo.

Per il secondo byte:

| bit |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| valore |

A7 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

A0 |

| note |

indirizzo |

La sequenza di eventi per i 10-bit è come indirizzo è analoga a

quella del modo a 7 bit:

- Ricevere per primo (alto) byte di indirizzo. SSPIF, BF e

UA (SSPSTAT <1>) vanno a 1.

- Occorre ora, obbligatoriamente, aggiornare il registro SSPADD con il secondo

byte (basso) di indirizzo. UA è cancellato automaticamente e

si rilascia la linea SCL.

- Occorre inoltre leggere il registro SSPBUF per cancellare il

flag BF e cancellare da programma il flag SSPIF.

Se questo byte non viene utilizzato, sarà scartato.

- A seguito dell' ACK generato dallo Slave, il Master

invia il secondo byte indirizzo. Alla ricezione, i flag SSPIF, BF e

UA vanno a 1

- Occorre ancora, obbligatoriamente, aggiornare il registro SSPADD con il

byte alto di indirizzo. UA, allora, è cancellato

automaticamente e si rilascia la linea SCL.

- Leggere il registro SSPBUF per cancellare BF e cancellare da

programma il flag SSPIF. Se questo byte non è utilizzato,

sarà scartato, ma può servire ad individuare l' indirizzo chiamato

nel caso in cui si applichi la mascheratura di indirizzo e lo Slave

possa rispondere a più di un indirizzo (ved. più avanti).

- A seguito dell' ACK inviato dallo Slave, il Master

invia una condizione di Restart. Lo Slave si predispone

alla ricezione di un byte.

- Il Master invia il primo byte (alto) di indirizzo. SSPIF

e BF vanno a 1.

In questo caso il bit R/W indicherà l' operazione richiesta

dal Master.

- Occorre ancora leggere il registro SSPBUF per cancellare BF e

cancellare da programma il flag SSPIF.

Note

Note

- Va compreso che il modulo MSSP compie automaticamente le

operazioni necessarie alla gestione hardware (rilevamento

dello Start e del Restart, generazione dell' ACK,

ricezione dei byte, comparazione degli indirizzi) e alle

segnalazioni per il software (attivazione dei flag e

cancellazione automatica di alcuni).

All' utente, però, resta la gestione della logica di

funzionamento del protocollo, del trattamento dei dati in

arrivo e della risposta alle segnalazioni dei flag e dell'

interrupt.

- E' indispensabile che il programma segua l' andamento della

comunicazione ed esegua le operazioni necessarie per

cancellare i flag di segnalazione.

UA indica la necessità di caricare SSPADD con l'

indirizzo della comparazione successiva.

Fino a che questo non viene fatto, lo Slave trattiene a

livello basso la linea SCL e il la comunicazione è

bloccata, dato che il Master riconosce questa condizione

come un clock stretching ed attende che lo Slave la

rimuova.

BF indica che un dato è in SSPBUF. Fino a che non si

opera la lettura del buffer, il flag BF resta a 1 e, a seguito

della ricezione di un successivo byte, scatta la condizione di

overflow (SSPOV=1). Con BF e/o SSPOV a 1, il modulo

MSSP non produce un ACK, ma un NACK !

La lettura di SSPBUF va fatta obbligatoriamente per

qualsiasi byte ricevuto. Se il dato non serve, si scarterà,

ma l' obbligo della lettura sussiste sempre. Non si tratta di

una condizione "inutile", ma del fatto che, in una

ricezione di dati, non è ammissibile la perdita di uno di

essi. BF indica che il software non ha recepito il

dato; di conseguenza il NACK comunica al Master la

mancata presa in carico dell' ultimo dato trasmesso. A questo

punto il Master potrà inviarlo nuovamente.

SSPIF indica che è avvenuto un evento significativo

che MSSP ha trattato in modo del tutto autonomo dall'

utente. E proprio per questo occorre che il programma prenda

visione dell' evento e lo tratti adeguatamente. La gestione è

possibile in polling, ma è altamente preferibile un interrupt,

abilitando il bit SSPIE, in modo da lasciare la CPU

libera di svolgere altre attività mentre MSSP cura la

comunicazione

- In base alle considerazioni ora esposte, dovrebbe essere

più chiaro perchè BF viene cancellato in automatico

alla lettura di SSPBUF e UA alla scrittura di SSPADD.

I due flag hanno indicato la carenza di una operazione e

quando l' utente lì'ha esguita, la loro funzione cessa e l'

automatismo di cancellazione ripsarmia una manovra al

programma.

Per contro, SSPIF, flag di interruzione, deve essere

cancellato volontariamente dopo che il software a servito

l' evento. La gestione dell' evento può essere più complessa

della semplice lettura o scrittura di un registro e quindi

deve essere svolta correttamente: alla sua fine, il flag di

chiamata potrà essere cancellato.

- Da notare che in tutti i casi, fino a che non si effettuano

le manovre richieste, i flag sono settati. In particolare, SSPIF

continuerà a richiedere interrupt fino a che non sarà

cancellato.

- In ultimo, se lo Slave al momento della ricezione della

condizione di Start iniziale è in overflow (BF/SSPOV=1),

ovvero non è stata trattata una condizione di errore

precedente, NON risponderà alla chiamata.

|

Mascheratura dell' indirizzo

Può essere utile, però, far rispondere lo Slave a più di un indirizzo; si

tratta di un microcontroller e quindi può svolgere diverse funzioni, ognuna

associata ad un indirizzo diverso sullo steso Slave.

Per arrivare a questo occorre fare si che una parte dei bit dell' indirizzo

dello Slave sia indifferente; questo si ottiene con la mascheratura.

La mascheratura di un bit di indirizzo provoca fa si che quel bit diventi

ininfluente (don ' t care). Quando un bit di indirizzo è mascherato, verranno riconosciuti

più indirizzi, che causeranno un interrupt.

È possibile mascherare più di un bit di indirizzo alla volta, il che rende possibile riconoscere fino a 31 indirizzi in modalità

a 7 bit e 63 in modalità a 10 bit.

Lo Slave I2C si comporta allo stesso modo, sia che il mascheramento

dell' indirizzo sia utilizzato, si che non venga effettuato. Tuttavia, quando viene utilizzato il mascheramento di indirizzo, lo

Slave riconosce come validi più indirizzi. Quando ciò si verifica, è necessario determinare quale indirizzo ha causato l'interrupt controllando il registro

SSPBUF.

Per il modo a 7 bit, i bit di mascheratura sono ADMSK <5:1>, che

mascherano i corrispondenti bit in SSPADD: per tutti i bit ADMSK che sono attivi (=

1), il bit corrispondente indirizzo viene ignorato (ADD = x).

Il modulo MSSP emetterà un ACK all' abbinamento degli indirizzi che non

sono mascherati.

Per il modo a 10 bit, vengono utilizzati ADMSK <5:2> per mascherare i bit di indirizzo corrispondente nel registro

SSPADD.

Inoltre, ADMSK<1> maschera contemporaneamente i due LSB <1:0>

dell'indirizzo.

Per tutti i bit ADMSK che sono attivi (= 1), il bit corrispondente indirizzo

viene ignorato (ADD = x).

Si noti inoltre che, anche se in modalità di indirizzamento a 10 bit, i bit due

bit superiori dell'indirizzo che utilizzano parte dei bit di registro SSPADD non

vengono mascherati; la mascheratura si indirizza solamente ai bit meno significativi.

Ad esempio:

- indirizzo a 7 bit

SSPADD<7:1> = 1010 0000

ADMSK<5:1> = 00 111

Indirizzi riconosciuti: 0xA0, 0xA2, 0xA4, 0xA6, 0xA8, 0xAA, 0xAC, 0xAE

- indirizzo a 10 bit

SSPADD<7:1> = 1010 0000 (A9:8 non sono mascherati in alcun caso)

ADMSK<5:1> = 00 111

Indirizzi riconosciuti: tutti quelli tra 0xA0 e 0xAF compresi

Ricezione in modo Slave

Vediamo in mod più approfondito la ricezione da parte dello Slave.

Quando il bit R/W del byte indirizzo inviato dal Master è a zero e si verifica un match di indirizzo, il bit di R/W del

registro SSPSTAT è cancellato, indicando che è stata richiesta una scrittura.

Lo Slave carica l'indirizzo ricevuto nel registro SSPBUF e la linea

SDA linea è

mandata a livello basso (ACK).

Da notare che se è stata verificata una condizione di overflow, non viene

generato l'impulso ACK, e, di conseguenza, ne risulta un NACK.

Una condizione di overflow è definita quando il flag

BF (SSPSTAT <0>) = 1, ovvero non è stato letto SSPBUF, oppure è a 1 il

bit SSPOV (SSPCON1<6>).

Per ogni byte di trasferimento dati, viene generato un interrupt settando SSPIF (PIR1<3>),

che deve essere cancellato da software.

Il registro SSPSTAT viene utilizzato per determinare lo stato del byte. Se è attivato il

SEN (SSPCON2<0>)

= 1, la linea SCL sarà mantenuta bassa dopo ogni trasferimento di

dati, operando un clock stretching; la linea va

liberata settando il bit CKP (SSPCON1<4>).

Una possibile sequenza di eventi per l' indirizzo a 7 bit senza clock

stretching (con SEN= 0) è esemplificata nel seguente diagramma:

- Un Master genera una condizione di Start. Il modulo MSSP dello Slave

rileva la condizione e pone il microcontroller in attesa.

-

In seguito alla condizione di Start, gli 8 bit inviati dal Master, campionati

sul fronte di salita del clock su SCL, sono shiftati nel registro SSPSR.

Sul fronte di discesa dell' ottavo impulso di clock, il valore del registro

SSPSR <7:1> viene confrontato con il valore del

registro SSPADD: se corrispondano e i bit BF e SSPOV sono a zero, sono

attivati i seguenti eventi:

- il valore in SSPSR viene caricato nel registro SSPBUF

- il flag di Buffer Full, BF, va a 1

- viene generato un impulso ACK.

Se BF e SSPOV non sono a 0, viene generato un NACK, che

comunica al Master l' impossibilità dello Slave di ricevere dati.

Perchè lo Slave possa riprendere la sua attività occorre che le

condizioni anomale siano rimosse.

Il flag di interrupt SSPIF (PIR1 3), è settato sul fronte di discesa del

nono impulso di clock (un interrupt viene generato, se abilitato).

Se SSPBUF viene letto, il flag BF è cancellato automaticamente. Invece

SSPIF va

cancellato da programma.

Il Master ha inviato il byte di indirizzo con R/W=0, ovvero indica

che scriverà dati sul bus, che lo Slave deve leggere.

- Il Master procede con l' invio del byte di dati.

- Completata la ricezione, SSPSR è copiato in SSPBUF, il flag BF va a 1 e

viene generato un ACK sul nono impulso del clock. SSPIF va a 1 per indiacre

il completamento dell' azione.

- Il Master invia un' altro byte, ma lo Slave non ha ancora letto il

precedente: BF è a 1

- All' arrivo dell' ottavo bit, il flag di overflow viene settato e nell'

impulso successivo del clock lo Slave genera un NACK

- Il Master chiude la trasmissione con uno Stop; il modulo MSSP dello

Slave

riconosce la condizione e passa in stato di inattività. Il bit P indica l'

evento

|

Se l' indirizzo è mascherato, ad esempio con ADMSK<5:1>

= 01 011, i bit ricevuti A1, A2, A4 saranno indifferenti.

Quindi lo Slave risponderà a più di un indirizzo.

Va osservato che, in questo caso, la lettura di SSPBUF ha anche lo

scopo di individuare l' indirizzo chiamato in modo tale che il programma

dello Slave agisca di conseguenza.

Per il resto, la ricezione avviene esattamente nel modo prima

delineato. |

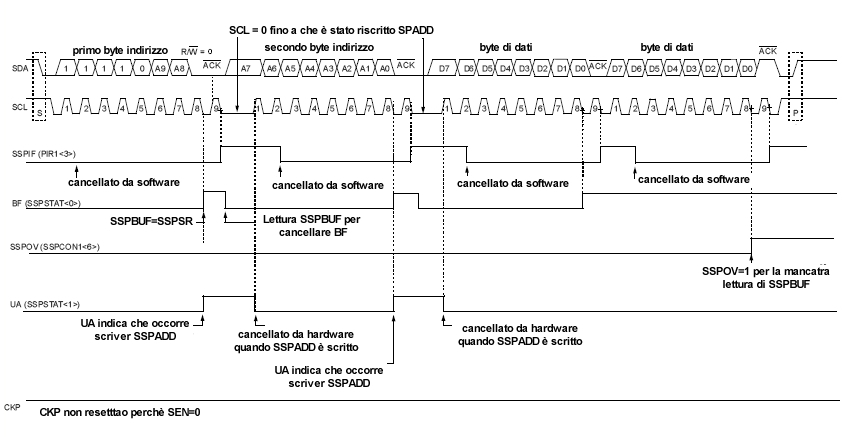

La ricezione con indirizzo a 10 bit è più complessa, essendo l' indirizzo

composto da due bytes successivi.

- Viene ricevuto il primo byte (alto) dell'indirizzo. Vengono settati

SSPIF, BF e

il flag UA (SSPSTAT<1>).

- Il software aggiorna SSPADD con secondo byte (basso) dell'indirizzo. Questo cancella bit UA e rilascia la linea

SCL.

- Il software legge SSPBUF, il che azzera il flag BF. Il

software cancella il flag SSPIF.

- Il modulo MSSP riceve il secondo byte (basso) dell'indirizzo. Vengono settati

SSPIF, BF e UA.

- Il software aggiorna SSPADD con il primo byte (alto) dell'indirizzo. Se

l' accoppiamento degli indirizzi è completato, si rilascia la linea SCL e

il flag UA viene azzerato.

- Il software legge SSPBUF, il che cancella il flag BF. Il

software cancella il flag SSPIF.

- Il Master invia un byte di dati.

- Il modulo MSSP dello Slave riceve il byte e genera un ACK. Vengono settati

SSPIF e BF.

- Il software dello Slave omette di leggere SSPBUF , per cui

BF resta a livello alto. Il software cancella il flag SSPIF.

- Il Master invia un secondo byte di dati, ma, siccome lo Slave non ha letto

il precedente, si genera un overflow e SSPOV va a 1

- Di conseguenza il modulo MSSP genera un NACK

- Il Master chiude la trasmissione con uno Stop

Il flag BF indica che SSPBUF è pieno e va letto prima di procedere oltre.

Questa operazione di lettura cancella automaticamente il flag stesso.

Va notato, anche, che

la lettura di SSPBUF durante la ricezione del secondo byte dell'

indirizzo a 10 bit ha lo scopo di verificare quale indirizzo è stato chiamato e

predisporre la risposta dello Slave. Ma anche nel caso in questo non sia

richiesto, occorre comunque effettuare l' operazione

per cancellare il flag BF ed evitare il settaggio del flag di overflow SSPOV. Se

la lettura del primo byte di indirizzo non ha altre funzioni, il byte letto viene semplicemente scartato.

Note:

- Va ben chiarito che, in ogni caso, il check tra i bytes di

indirizzo, 1 per il modo a 7 bit e 2 per il modo a 10

bit, inviati dal Master, e quello proprio dello Slave, è

effettuato dall' hardware dell' MSSP in modo del tutto automatico.

La lettura del contenuto di SSPBUF, è invece, a carico del

software ed è obbligatoria per evitare l' overflow. Se il

dato di indirizzo letto ha utilità per il programma, sarà

trattato opportunamente, altrimenti sarà ignorato.

-

Da osservare che l' utente deve avere caricato in SSPADD il primo byte dell'

indirizzo, ricevuto e confermato il quale deve caricare nello stesso registro il

secondo byte perchè il modulo MSSP possa effettuare la comparazione completa.

Così pure, ricevuto la seconda parte dell' indirizzo, SSPADD deve essere ri

aggiornato con la prima parte, in modo da essere pronto per una futura

comparazione.

Questo deve accadere sia che la comparazione dell' indirizzo sia andata a buon

fine o meno. Fino a che SSPADD non viene ricaricato, la linea SCL resta a

livello basso.

-

Il flag SSPOV deve assolutamente essere cancellato dal programma. Se si ha ragione di credere che sia possibile che il programma

risponda rapidamente a un evento, è consigliabile verificare sempre SSPOV.

-

Se i flag non sono cancellati, si verificano condizioni che abortiscono la

comunicazione.

Quindi occorre sempre intervenire con la giusta tempistica a leggere SSPBUF,

il che cancella BF ed evita il settaggio di SSPOV e, nella fase di

indirizzamento, aggiornare SSPADD seguendo le richieste espresse da UA

Questa necessità di controllo adeguato sulla comunicazione rende una

gestione in bit banging o in polling tale da tenere occupato il microcontroller

praticamente solo con questa task. Solo una gestione in interrupt permette

di avere spazio per altre operazioni.

-

Se si è abilitata la ricezione della General Call occorrerà che il firmware

sia stato scritto per trattare adeguatamente questo evento.

|

Il flag UA indica che l' interrupt di SSPIF è dovuto all' arrivo della prima

parte dell' indirizzo e occorre caricare la seconda. UA torna a 1 dopo la

ricezione della seconda parte per indicare che occorre aggiornare SSPADD.

Questo flag si cancella

automaticamente quando viene scritto SSPADD.

Nelle fasi 7-10 dell' esempio, il Master, dopo aver indirizzato lo Slave a 10

bit, procede all' invio di un dato: questo byte potrà essere un indirizzo interno dello Slave a cui il Master deve

accedere oppure un comando per lo Slave.

Essendo già stato identificato l'indirizzo dello Slave, il flag UA non viene

più toccato, mentre è in azione la normale sequenza di SSPF= BF=1 per indicare

che un dato è stato ricevuto e occorre leggere il buffer.

Come nel caso precedente, la mancata lettura del dati in SSPBUF crea una

situazione di overflow e la generazione di un NACK invece di ACK.

Il Master potrà chiudere la comunicazione con uno Stop, lasciando libero il bus

oppure ripartire con un Restart, mantenendo il controllo sul bus.

La situazione è identica all' esempio precedente nel caso di mascheratura

dell' indirizzo.

|

Se l' indirizzo è mascherato, ad esempio con ADMSK<5:1>

= 01 001, i bit ricevuti A0, A1, A4 saranno indifferenti.

I bit A9:8 non possono essere mascherati.

In questa condizione, lo Slave risponderà a più di un indirizzo.

Va osservato che la lettura di SSPBUF ha anche lo

scopo di individuare quale è esattamente l' indirizzo chiamato in modo tale che il programma

dello Slave agisca di conseguenza.

Per il resto, la ricezione avviene nel modo prima

delineato.

|

Trasmissione in modo Slave

Se il Master invia l' indirizzo dello Slave con il bit 0 (R/W) =

1, indica

che si tratta di una richiesta di dato che lo Slave dovrà trasmettere.

Il diagramma seguente rappresenta un esempio di comunicazione con lo Slave a 7

bit di indirizzo:

- Il Master trasmette l' indirizzo dello Slave. Gli 8 bit sono shiftati in

SSPSR.

- Quando il bit R/W è a 1 e si verifica un match di indirizzo, viene

settato il bit R/W del Registro SSPSTAT dello Slave.

- L'indirizzo ricevuto viene caricato dal modulo MSSP nel registro SSPBUF. e

viene generato automaticamente l'impulso ACK in corrispondenza del nono bit

del clock inviato dal Master sulla linea SCL.

- SCL è mantenuta bassa dallo Slave indipendentemente dallo stato del

bit SEN di stretch del clock.

- Il bit SSPIF è settato sul fronte di discesa del nono impulso di clock.

Occorre che il software dello Slave cancelli questo flag per liberare la

linea SCL. SCL deve essere abilitato impostando bit CKP.

- Lo Slave invia i dati su SDA, mentre il Master fornisce il clock su

SCL.

La trasmissione del byte si chiude con la generazione da parte del Master

dell' ACK. L'impulso ACK dal Master-ricevitore è agganciato sul fronte di

salita del nono impulso di clock.

- Avendo ricevuto un ACK, lo Slave procede con un successivo invio. Ancora una volta, pin

SCK/RC3/SCL deve essere abilitato impostando bit CKP.

- Il Master non richiede altri dati e mette la linea SDA in NACK

(SDA=1), ad

indicare che il trasferimento dei dati è completo. In questo caso, quando NACK è agganciato

dallo Slave, la logica del modulo MSSP viene disattivata e SSPSTAT resettato. Il

modulo MSSP dello Slave passa in attesa di un nuovo stato di Start.

Per ogni byte di trasferimento dati, viene generato un interrupt; il bit SSPIF deve essere cancellato nel software e registro

SSPSTAT viene utilizzato per determinare lo stato del byte.

Nel modo di indirizzamento a 10 bit le condizioni sono analoghe, solamente

sarà più laboriosa la ricezione dei bytes dell' indirizzo.

Osservare che il bit R/W del primo byte di indirizzo è a zero

per la scrittura del secondo byte, mentre il terzo byte di indirizzo è

copia del primo con R/W a livello 1 per indicare la lettura.

|