Il modo PWM

Nei dispositivi PIC18F4221/4321, CCP1 è implementato come

modulo con funzionalità Enhanced PWM.

Questi includono 2 o 4 canali di output, con polarità selezionabile

dall'utente, controllo della dead band e spegnimento e riavvio

automatico.

Queste funzioni sono disponibili, per la famiglia in esame, nei dispositivi

in package a 40/44 pin, ma non in quelli a 28 pin. |

Le funzioni base, come catturare e confrontare e la singola uscita PWM,

nel modulo Enhanced (ECCP) sono le stesse descritte prima per il modulo

CCP.

Il registro di controllo dell' Enhanced CCP si differenzia dai registri

CCPxCON in PIC18F2221/2321 perché i due bit più significativi vengono

ora implementati per controllo delle nuove funzionalità PWM.

Il registro CCP1CON

è organizzato nel seguente modo:

| CCP1CON |

bit |

P1M1 |

P1M0 |

DC1B1 |

DC1B0 |

CCP1M3 |

CCP1M2 |

CCP1M1 |

CCP1M0 |

| funzione |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| default |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

,6 P1M1:0

:

bit di configurazione modo ECCP

se CCP1M3:2

= 00, 01 o

10

xx

=

P1A è il pin di input capture/compare, P1B, C, D sono I/O

se CCP1M3:2

= 11

00

= singola uscita su P1A. P1B, C, D sono I/O

01

= full bridge forward: P1D pwm, P1A attivo; P1B, C inattivi

10

= uscita half bridge: P1A,B pwm con dead band; P1C, D sono I/O

11

= full bridge reverse: P1B pwm; P1C attivo; P1A, B inattivi

bit

5,4

DC1B1:0

:

Duty cycle del PWM

sono i due LSb del modo PWM a 10 bit; gli altri 8 bit sono i CCPR1L

Non

usati in modo capture e compare

bit

3,0

CCP1M3:0

: selezione della modalità operativa

0000 = ECCP disabilitato e reset del modulo

0001

= riservato

0010

= modo Compare, inversione uscita al match

0011

= modo Capture

0100 = modo Capture, fronte di discesa

0101 = modo Capture, fronte di salita

0110 = modo Capture ogni quarto fronte di salita

0111 = modo Capture ogni sedicesimo fronte di salita

1000 = modo Compare, inizializza CCP1 basso, set output al match

1001 = modo Compare, inizializza CCP1 alto, clear output al match

1010 = modo Compare, genera interrupt software

1011 = modo Compare, special event trigger

1100 = modo PWM; P1A, B, C, D attivi alto

1101 = modo PWM; P1A, C attivi alto - P1B, D attivi basso

1110 = modo PWM; P1A, B attivi basso- P1C, D attivi alto

1111 = modo PWM; P1A, C attivi basso - P1B, D attivi basso

Oltre alla gamma estesa di modalità disponibili attraverso i registri di

CCP1CON ed ECCP1AS, il modulo ECCP ha un registro aggiuntivo associato alle

operazioni di Enhanced PWM e alla funzionalità di auto-spegnimento, che è ECCP1DEL.

Configurazione del modulo ECCP

Il modulo Enhanced CCP può avere fino a quattro uscite PWM, in base alla

modalità operativa selezionata.

Queste uscite, indicate da P1A a P1D, sono multiplexate su PORTC e PORTD.

Le uscite attive dipendono la modalità operativa di CCP selezionata.

Le assegnazioni dei pin sono riassunti nella tabella seguente.

| modo

ECCP |

configurazione

CCP1CON |

RC2 |

RD5 |

RD6 |

RD7 |

modo compatibile

CCP |

00xx 11xx |

CCp1 |

RD5/PSP5 |

RD6/PSP6 |

RD7/PSP7 |

| dual PWM |

10xx 11xx |

P1A |

P1B |

RD6/PSP6 |

RD7/PSP7 |

| quad PWM |

x1xx 11xx |

P1A |

P1B |

P1C |

P1D |

Per configurare il pin come uscita del PWM è necessario selezionare la

corretta modalità PWM impostando il bit CCP1M3:0 e

P1M1:0.

Occorre

inoltre aver

designato come uscite i pin nei registri TRISC e TRISD.

Se i pin di uscita non sono selezionati come tali nei

registri di direzione, il modulo PWM funziona regolarmente, ma non è

presente alcun segnale sui pin.

|

Quando configurato in modalità singola uscita, le funzioni del modulo

ECCP sono identiche a quelle del modulo standard CCP. Questo è anche

indicato come modalità "CCP compatibile"

Come per i moduli standard di CCP, il modulo ECCP può utilizzare

Timer1,

2 o 3, dipendentemente dalla modalità selezionata. Timer2 e Timer3 sono

disponibili per i modi di cattura e confronto, mentre Timer2 è

disponibile per i modi PWM. Le interazioni tra i timer sono identiche a

quelle descritte per moduli standard di CCP.

Fatta eccezione per l'operazione del Trigger di evento speciale, anche le

modalità di acquisizione e confronto del modulo ECCP sono identiche in

funzione a quella di CCP2. Quindi, in questo senso non sono necessarie

modifiche al software quando si passa da dispositivi con moduli CCP a

dispositivi con moduli ECCP (da 28-pin a 40/44-pin nel caso della famiglia

in esame).Nel modo con trigger per evento speciale, l'output di trigger di ECCP1

reimposta il Timer1 o il Timer3, a seconda di quale timer è selezionato. Questo

permette il registro CCPR1 di essere efficacemente un registro di periodo a

16 bit programmabile per Timer1 o Timer3.

Modo Enhanced PWM

Come abbiamo visto, la modalità Enhanced PWM fornisce ulteriori opzioni di

output PWM per una più ampia gamma di applicazioni di controllo, in

particolare per la gestione di ponti (bridges).

Il modulo offre fino a quattro uscite, di cui gli utenti sono anche in

grado di selezionare la polarità (attivo alto o attivo basso), impostando P1M1:0 e

CCP1M3:0 di CCP1CON. Il diagramma a blocchi

seguente mostra uno schema semplificato del funzionamento del PWM.

Tutti i registri sono a doppio buffer al fine di prevenire glitch su una

qualsiasi delle uscite e vengono caricati all'inizio di un nuovo PWM.

Il solo registro di ritardo della dead band, ECCP1DEL, viene caricato al

termine del ciclo o del periodo. A causa del buffering, il modulo attende fino

al termine del timer assegnato, invece di iniziare immediatamente. Questo

significa che forme d'onda Enhanced PWM non corrispondono esattamente alle

forme d'onda PWM standard, ma è invece compensato dal ciclo completo di una istruzione (4 TOSC).

Il Periodo del PWM è calcolabile come :

Periodo PWM = [(PR2)+1] * 4 * Tosc * (Prescaler TMR2)

Si ricorda che anche qui il post scaler di Timer2 non viene utilizzato.

Quando TMR2 è uguale a

PR2 si verificano i seguenti tre eventi :

- TMR2 è azzerato

- il pin CCP1 è portato a 1 (fa eccezione il caso in cui il Duty Cycle

sia posto a 0)

- il Duty Cycle del PWM è copiato da CCPR1L

a

CCPR1H

Il Duty Cycle del PWM viene specificato scrivendo il registro CCPRxL (8 bit

più significativi) ed i bit CCP1CON<5:4> (2 bit meno significativi),

per un totale di 10 bit di risoluzione.

Il valore del Duty Cycle è dato dalla seguente espressione :

Duty Cycle PWM = (CCPR1L:CCP1CON<5:4>) * Tosc *

(Prescaler TMR2)

CCPR 1L e

CCPR1CON<5:4> possono essere scritti in qualsiasi

momento, ma il valore imposto al Duty Cycle non viene trasferito in CCPR1H

se

non dopo una uguaglianza tra PR2 e TMR2,

ovvero quando il periodo è completato.

Nel modo PWM, il registro CCPR1H

è a sola lettura; il

registro CCPR1H

e il latch dei 2 LSbit vengono utilizzati per il doppio buffer del duty cycle

PWM. Questo doppio buffering è essenziale per il funzionamento edr

ha lo scopo di evitare impulsi spuri (glitches) nel segnale PWM.

Quando CCPR 1H

e il latch dei due bit minori eguaglia

TMR2, concatenato con

un Q clock interno a 2 bit o con il prescaler di TMR2, il pin

CCP1 è portato

a 0.

La massima risoluzione in bit del PWM è data dalla seguente espressione :

Risoluzione massima PWM = log(Fosc/Fpwm) / log(2)

La tabella seguente da una idea delle possibilità :

| Frequenza del PWM |

2.44kHz |

9.77kHz |

39.6kHz |

158.25kHz |

312.5kHz |

416.67kHz |

| Prescaler del Timer2 |

16 |

4 |

1 |

1 |

1 |

1 |

| Valore in PR2 |

FFh |

FFh |

FFh |

3Fh |

1Fh |

17h |

| Massima risoluzione (bit) |

10 |

10 |

10 |

8 |

7 |

6.58 |

Da osservare che, nel caso in cui erroneamente il Duty Cycle del PWM sia stato impostato di valore

maggiore del periodo, il pin CCP1 non cambierà stato.

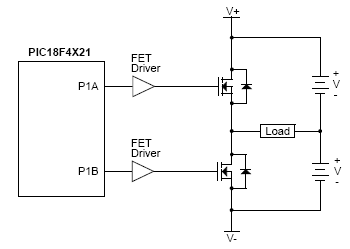

Uscite del PWM - Half bridge

Una delle modalità programmabili prevede due uscite, P1A e P1B.

I diagrammi seguenti chiariscono i rapporti tra i segnali, i primi prima relativamente alle uscite attive nello stato

alto

i secondi, per quelle attive nello stato basso

La disponibilità di due uscite consente di utilizzare

diverse tipologie di buffer, ad esempio un half-bridge, di cui vediamo

una schematizzazione nell' immagine seguente.

|

Si tratta di un classico semi-ponte (half-bridge), costituito da due MOSFET N che

azionano un carico con doppia alimentazione.

Le uscite P1A e P1B, attraverso buffer adeguati, pilotano i gate dei

MOSFET.

Il carico (load) potrà essere tanto un elemento induttivo (motore in CC,

solenoide, ecc) quanto un

elemento resistivo (riscaldamento, illuminazione, ecc). I diodi di

proteggono i semiconduttori dai picchi inversi di tensione. |

In modalità Half-Bridge, i due pin di uscita vengono utilizzati per

pilotare carichi in push-pull. Il segnale di uscita PWM è sul pin P1A,

mentre il segnale di uscita PWM complementare è su P1B.

Da osservare l' introduzione di drive per il gate dei MOSFET, ad esempio Maxim

MAX4427 o meglio Microchip TC4424, in grado di fornire impulsi di corrente da

3A.

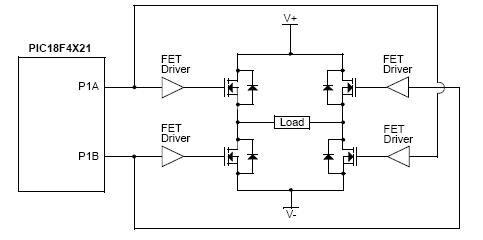

E una struttura del genere potrà pilotare anche un ponte intero

|

Osserviamo come l' incrocio delle uscite PWM vada ad operare su MOSFET

di rami opposti del ponte intero, che ora richiede 4 semiconduttori di

potenza e 4 buffer-driver. In questo modo quattro

interruttori

possono

essere modulati con due segnali PWM.

La tensione di alimentazione ora potrà essere singola.

Si ricorda che il buffer-driver sono necessari per pilotare MOSFET di

potenza che non abbiano gate logic level. |

In modalità Half-Bridge, il ritardo programmabile della dead band può

essere usato per prevenire il shoot-through di corrente nei semiconduttori di

potenza del mezzo ponte. Il valore dei bit PDC6:PDC0, imposta il numero di

istruzioni cicli prima che l'output sia portato attivo.

Se il valore è

maggiore di duty cycle, l'output corrispondente rimane inattivo durante

l'intero ciclo.

E' opportuno ricordare ancora

che le uscite P1A e P1B sono multiplexate con PORTC 2 e PORTD 5 e le

relative altre funzioni programmabili; quindi occorre che il TRISC 2 e TRISD 5

siano impostati a zero (come uscita) per ottenere ai pin il segnale PWM.

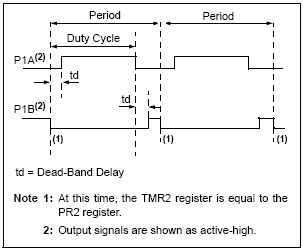

Il diagramma seguente riporta l' andamento dei segnali:

|

Osserviamo che i segnali presenti su P1A e P1B sono complementari

(opposti).

Inoltre può venire aggiunto il tempo td di dead band in cui si

ritarda la conduzione di uno dei semiconduttori di potenza onde evitare

che che si formi un pericoloso corto circuito tra i due poli dell'

alimentazione dovuto alla contemporanea conduzione dei due MOSFET.

Osserviamo, quindi, come il modulo ECCP consenta una gestione

avanzata dei ponti in PWM senza la necessità di altri componenti sterni

se non i driver per i semiconduttori di potenza. |

Uscite del PWM - Full bridge

In modalità Full-Bridge, sono utilizzati come uscite 4 pin,

attivi a coppie.

In modalità Forward, pin P1A è costantemente attivo e pin P1D è modulato

dal PWM.

In modalità Reverse, pin P1C è costantemente attivo e pin P1B è modulato

dal PWM.

I diagrammi seguente illustrano l' andamento dei segnali.

Anche qui occorre ricordare che P1A, P1B, P1C e P1D sono

multiplexati con le altre funzioni

programmabili sul PORTC 2 e PORTD <7:5>; per ottenere

in uscita i segnali PWM su questi pin occorre aver programmato TRISD

<7:5> e TRISC 2 a livello 0 in modo da rendere uscite digitali i pin

corrispondenti. Se questo non viene fatto, il modulo PWM opererà

correttamente, ma nessun segnale di uscita sarà disponibile sui pin.

L' applicazione tipica è il comando di un full bridge a 4 segnali

distinti.

In modalità Full-Bridge, il bit P1M1 nel registro

CCP1CON permette all'

utente di controllare la direzione avanti / indietro. Quando il firmware

cambia questo bit di controllo di direzione, il modulo assumerà la nuova

direzione nel prossimo ciclo di PWM.

Poco prima della fine del periodo corrente, le uscite modulate (P1B e

P1D)

sono portate nel loro stato inattivo, mentre le uscite P1A e

P1C sono accese.

Questo si verifica in un intervallo di tempo di

4 TOSC * (Timer2 valore Prescaler)

prima che inizi il prossimo periodo PWM. Il prescaler di Timer2 sarà 1, 4 o

16, dipendemente dal valore dei bit T2CKPS1:0

(T2CON<1:0>).

Il diagramma seguente presenta l' andamento dei segnali al cambio di

direzione.

Si noti che in modalità Full-Bridge, il modulo ECCP1 non fornisce alcun

ritardo dead band, dato che, in generale, una sola uscita è modulata

dal PWM. Tuttavia, c'è una situazione

in cui un ritardo potrebbe essere richiesto. Questa situazione si

verifica quando entrambe le seguenti condizioni sono vere:

Figura seguente mostra un esempio in cui la direzione PWM cambia vicino al

100% duty cycle.

Al tempo t1, le uscite P1A e P1D

diventano inattive, mentre l'output P1C diventa attivo.

In questo esempio, poiché il tempo di spegnimento dei dispositivi di potenza è

più lungo del tempo di accensione, una corrente può fluire attraverso i

dispositivi di potenza QC e QD dello schema di principio presentato più sopra.

E questo per la durata del ' t '. Lo stesso fenomeno si verifica per i

dispositivi di potenza QA e QB per il cambio di direzione opposto. Dunque, se

un cambio di direzione con un alto duty cycle è necessaria per l'applicazione,

è necessario ricorre ad una delle seguenti misure:

- ridurre PWM per un periodo prima dei cambi di direzione.

- utilizzare i driver che possono guidare gli switch off più velocemente

di quanto essi possono raggiungere il livello alto.

Dead Band programmabile

Nelle applicazioni di mezzo ponte, dove tutti gli switch di potenza sono

modulati alla frequenza PWM, gli interruttori a semiconduttore normalmente richiedono più tempo per

spegnersi rispetto a quello necessario per passare in conduzione.

Se uno degli interruttori di potenza superiore e inferiore viene spento

contemporaneamente all' accensione dell' altro, entrambi possono trovarsi in

conduzione per un breve periodo, durante il quale una corrente molto elevata (shootthrough

corrente) può fluire attraverso entrambi i semiconduttori. Si tratta

sostanzialmente di un corto circuito sulla tensione di alimentazione in cui la

bassissima resistenza di conduzione dei transistor o MOSFET consente il

passaggiuo di correnti così elevate da distruggerne le giunzioni.

Per evitare questo effetto potenzialmente distruttivo, la tecnica a cui si

ricorre è quella di inserire un ritardo all' avvio di uno switch per

consentire all'altro semiconduttore di disattivarsi completamente.

In modalità Half-Bridge, il ritardo, denominato dead band, è

programmabile e si applica sulla transizione del segnale dallo stato

non attiva allo stato attivo.

I bit PDC6:0 del registro ECCP1DELstabiliscono il ritardo in termini di cicli di istruzione del microcontrollore

(4 TOSC).

Va ricordato che, non essendo le funzioni enhanced disponibili nei chip a 28

pin (18F2221/2321 ), questo regsitro esiste solo nei dispositivi a 40/44 pin

(18F4221/4321).

Il registro ECCP1DELCON

è organizzato nel seguente modo:

|

ECCP1DELCON |

bit |

PRSEN |

PDC6 |

PDC5 |

PDC4 |

PDC3 |

PDC2 |

PDC1 |

PDC0 |

| funzione |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| default |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

PRSEN

:

bit di abilitazione del restart del PWM

1

= il bit ECCPASE si cancella automaticamente una volta che l'evento

shutdown

è terminato; il PWM si riavvia automaticamente

0

= il bit ECCPASE deve essere cancellato via software per riavviare il

PWM

bit

6,0

PDC6:0

: bit di conteggio del ritardo

Tempo di dead band, in numero di FOSC/4 (4 * TOSC) cicli, tra il

tempo effettivo e quello impostato

per la transizione attiva del PWM

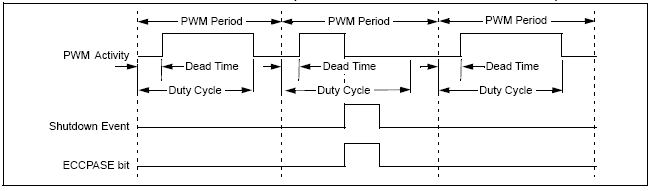

ENHANCED PWM AUTO-SHUTDOWN

Quando il ECCP1 è stato programmato per una qualsiasi delle modalità

Enhanced PWM, il pin di uscita attivo può essere configurato per lo spegnimento

automatico a seguito di un evento. L' autospegnimento (auto-shutdown) pone immediatamente il pin di uscita PWM

in uno stato definito (programmabile) quando si verifica l' evento di arresto.

Va aggiunto che è possibile programmare sia una situazione di auto-shutdown,

sia una situazione di auto-shutdown con riavvio automatico (restart).

Il diagramma seguente presenta i segnali in caso di auto shutdown con auto

restart abilitato.

e con auto restart disabilitato

Un evento di arresto può essere causato da

- uno dei moduli comparatore

- un

basso livello sul pin di ingresso (FLT0)

- o qualsiasi combinazione di

queste tre fonti.

Ad esempio, i comparatori possono essere utilizzati per seguire un input di tensione

proporzionale ad una corrente monitorata nel circuito ponte, realizzando una

limitazione di corrente automatica. Se la tensione supera una soglia, il comparatore interruttori stato e

innesca un arresto.

In alternativa, un livello basso sul pin FLT0 può arrestare il PWM.

La funzione di spegnimento automatico, ovviamente, può essere anche disattivata.

Le

fonti di auto-shutdown sono selezionate utilizzando i bit

ECCPAS2:ECCPAS0 (ECCP1AS <6:4>).

Quando si verifica un arresto, il pin

di uscita sono in modo asincrono collocati nei rispettivi Stati di arresto,

specificato dai bit PSSAC1:PSSAC0 e PSSBD1:PSSBD0 (ECCP1AS <3:0>). Ogni

coppia di poli (P1A/P1C e Florez / P1D) può essere impostato per guidare

alta, guidare basso o essere tri-ha dichiarato (non di guida). Il ECCPASE bit

(ECCP1AS 7) è anche insieme a tenere il PWM Enhanced uscite nei rispettivi

Stati di arresto. Il bit ECCPASE è impostato dall'hardware quando si verifica

un evento di arresto.

Se non è impostato il riavvio automatico, il bit ECCPASE deve essere

cancellato dal firmware quando si cancella la causa dell' arresto. Se è

attivato il riavvio automatico, il bit ECCPASE è cancellato automaticamente

quando la causa di auto-spegnimento è deselezionata.

Se viene impostato il

bit ECCPASE quando inizia un periodo PWM, le uscite PWM rimangono nel loro

stato inattivo per quel periodo PWM intero. Quando il bit ECCPASE è

deselezionato, le uscite PWM ritornerannoa al funzionamento normale all'inizio

del prossimo periodo PWM.

La scrittura di ECCPASE è disabilitata fintanto che una condizione di

shutdown è attiva. |

Il registro che controlla queste operazioni è ECCP1AS, organizzato nel seguente modo:

| ECCP1AS |

bit |

ECCPASE |

ECCPAS2 |

ECCPAS1 |

ECCPAS0 |

PSSAC1 |

PSSAC0 |

PSSBD1 |

PSSBD0 |

| funzione |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| default |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

- bit 7

ECCPASE

:

bit di evento di auto shutdown

1

= evento shutdown - le uscite sono in stato di shutdown

0

= uscite operative

- bit

6,4

ECCPAS2:0

: bit di selezione della sorgente di auto shutdown

111 =

FLT0 o Comparatore 1 o Comparatore 2

110 =

FLT0 o Comparatore 2

101 =

FLT0 o Comparatore 1

100 =

FLT0

011 =

Comparatore 1 o Comparatore 2

010 =

Comparatore 2

001 =

Comparatore 1

000 =

disabilitato

- bit

3,2

PSSAC1:0

: bit di controllo shutdown pin A e C

1x =

pin A e C in tri-state

01 =

pin A e C a livello 1

00 =

pin A e C a livello 0

- bit

3,2

PSSBD1:0

: bit di controllo shutdown pin B e D

1x =

pin B e D in tri-state

01 =

pin B e D a livello 1

00 =

pin B e D a livello 0

Va ricordato che, non essendo le funzioni enhanced disponibili nei chip a 28

pin (18F2221/2321 ), questo registro esiste solo nei dispositivi a 40/44 pin

(18F4221/4321).

Considerazioni allo startup

Quando il modulo ECCP è utilizzato in modalità PWM, l'hardware della

applicazione deve utilizzare i corretti pullup e/o pull-down esterni per i pin di uscita

PWM, a seconda del carico comandato.

Quando il microcontroller è rilasciato dal Reset, tutti i

pin di I/O sono nello stato ad alta impedenza; ne consegue che i circuiti esterni devono tenere

i dispositivi di commutazione in stato OFF fino a quando il programma nel

microcontroller prende il comando dei pin con i livelli di segnale corretto o attiva

l' uscita PWM.

I bit di CCP1M1:CCP1M0 (CCP1CON <1:0>) permettono

all'utente di scegliere se i segnali di uscita PWM sono attivi a livello alto o

basso per ogni coppia di pin di uscita PWM (P1A/P1C e P1B/P1D).

Le polarità devono essere selezionate prima che i pin del PWM

siano configurati come

uscite.

Modifiche della configurazione di polarità, mentre i pin PWM sono

configurati come uscite, non è consigliabile, poiché può provocare danni ai

circuiti collegati. |

Se P1A, P1B, P1C e P1D non sono nello stato corretto quando viene inizializzato il modulo

PWM possono risultare, anche se per breve tempo, stati di conduzione

inapproppriati negli elementi di potenza che

potrebbero danneggiare il circuito di applicazione.

Il modulo ECCP deve essere attivato in modalità di uscita corretta e completare un ciclo completo di PWM

prima di configurare i pin PWM come uscite. Il completamento di un ciclo di PWM viene indicato

dal bit TMR2IF.

Setup del PWM

Per il setup del modulo ECCP in PWM occorre:

- Configurare i pin PWM, P1A e P1B ( P1C e P1D), se usato

come input impostando i bit TRIS corrispondenti.

- Impostare il periodo PWM

caricando il registro PR2.

-

Se è necessario l' auto-shutdown, effettuare le

seguenti operazioni:

• disabilitare l' auto spegnimento (ECCPASE = 0)

• configura l' origine (FLT0, comparatore 1 o 2)

• aspettare per la

condizione di non-arresto

- Configurare il modulo ECCP per la modalità PWM

desiderata caricando il CCP1CON con i valori

appropriati:

• selezionare una delle configurazioni di uscita disponibile e

direzione con i bit P1M1:P1M0.

• selezionare la polarità dei segnali di

uscita PWM con i bit CCP1M3:CCP1M0.

- Impostare il ciclo caricando

il registro CCPR1L e CCP1CON <5:4> .

- Per una uscita Half-Bridge,

impostare il deadband con ECCP1DEL <6:0>

- Se l'operazione di spegnimento automatico è necessaria,

caricare il registro ECCP1AS:

• selezionare le fonti di auto spegnimento

utilizzando i bit ECCPAS2:ECCPAS0.

• selezionare gli Stati di arresto dei pin

uscita PWM utilizzando il PSSAC1:PSSAC0 e il PSSBD1:PSSBD0 bit.

• Impostare il

bit ECCPASE (ECCP1AS 7).

• configurare i comparatori utilizzando il CMCON

• configurare gli ingressi del comparatore come ingressi analogici.

- Se

l'operazione di riavvio automatico è necessaria, impostare il bit PRSEN

(ECCP1DEL7).

- Configurare e avviare TMR2:

• deselezionare il flag di interrupt del timer con il bit TMR2IF (PIR1 1).

• impostare il valore di

prescaler di TMR2 caricando i bit T2CKPS (T2CON <1:0>).

• abilitare Timer2 il bit TMR2ON (T2CON 2).

- Abilitare le uscite PWM dopo un ciclo PWM:

• attendere fino al TMRn overflow (è impostato il bit TMRnIF).

• abilitare il CCP1/P1A, P!B, P1C e/o P1D deselezionando i

rispettivi bit TRIS.

• cancellare il bit ECCPASE (ECCP1AS 7).

Operazioni in Power Managed

In Sleep mode, le fonti di clock sono disabilitate, per cui il Timer2 non

sarà incrementato e lo stato del modulo ECCP non cambierà.

Se il pin ECCP è utilizzato come uscita, continuerà mantenere il livello a cui

è stato fissato.

Se sono attivate

due velocità di start-up, la frequenza di avviamento iniziale da INTOSC e il

postscaler non potranno essere stabili immediatamente. In modalità PRI_IDLE, il

clock primario continuerà ad alimentare il modulo ECCP senza cambiamento.

Altri clock di modalità di gestione del consumo energetico molto

probabilmente saranno diversi come frequenza da quella prevista per Timer2, che

dipende dal clock primario.

Se il monitor fail-safe del clock è

attivato, un problema al clock forzerà il dispositivo nella modalità di

gestione del consumo energetico RC_RUN e il OSCFIF bit (PIR2 7) verrà

impostato. ECCP sarà clockato dall' oscillatore

interno, che potrà una frequenza di clock diverso rispetto al

primario.

Un Power-on Reset e successive reimpostazioni costringeranno tutte

le porte alla modalità di input e porteranno i vari registi alle condizioni di

default, in particolare porterà il modulo ECCP in modalità di compatibilità

con CCP.

I registri interessati al PWM

Il foglio dati riporta come al solito un elenco dei registri che sono

interessati dalle operazioni del modulo ECCP per le operazioni di PWM.

Il fondo bianco delle celle della Tab.15-3 identifica quali registri e bit

vanno considerati quando si affronta la programmazione (mentre le celle con

fondo grigio indicano bit o registri non interessati).

La gestione dei bit dei registri PIR/IPIR/PIE

per l' interrupt riguarda il Timer2 e sarà considerata dove necessaria,

sempre ricordando che i flag dei registri PIR

sono testabili anche in polling e vanno azzerati da programma quando

necessario.

La collocazione dei flag e dei bit nei registri suddetti indica che gli

interrupt di Timer2 fanno parte del gruppo dei periferici e la loro chiave di

abilitazione, nel caso di interrupt senza priorità, è il bit PEIE

di INTCON.

|