PORTA

PORT A è un registro a 8 bit per uso generico (GPIO

- General Purpose IO) a cui sono solitamente associate parecchie funzioni

alternative, in particolare quelle di ingresso del modulo convertitore

analogico/digitale (AD).

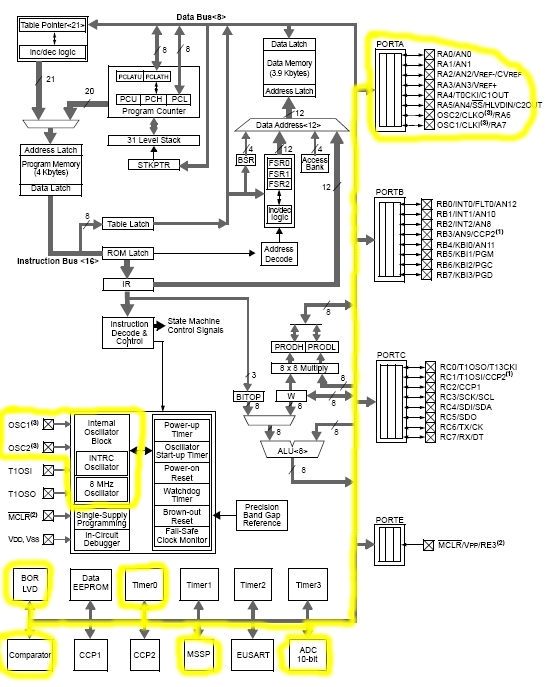

Possiamo evidenziare, sullo schema di principio del

microcontroller, le aree che interessano PORTA e che si possono riassumere

in:

-

funzione generale di I/O digitale

-

ingressi del modulo di conversione analogico/digitale

(AD)

-

comparatori analogici

-

tensione di riferimento del modulo AD e dei

comparatori

-

ingresso del modulo HLVD

-

ingresso esterno del TIMER0 (come contatore)

-

ingresso SS del modulo MSSP (come Slave)

-

ingresso/uscita dell' oscillatore principale

Nello schema di principio del controller, mettiamo in

evidenza il PORTA e i circuiti associati:

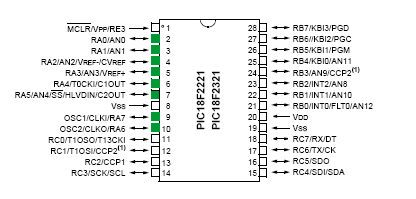

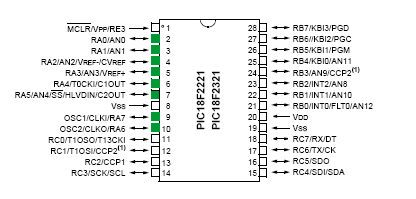

Fisicamente i pin si trovano qui:

|

Microchip mantiene un ragionevole senso nella disposizione delle

funzioni cercando di porle in modo successivo in corrispondenza dei

pin.

Va notato che RA7 e RA6 sono funzioni "secondarie" dei

pin 9 e 10, in quanto essi sono previsti per l' oscillatore. Però,

dato che i PIC18 dispongono di un ampio spettro di possibilità di

funzionamento con l' oscillatore integrato, senza elementi

esterni, questi pin possono essere rilasciati a completare

PORTA. |

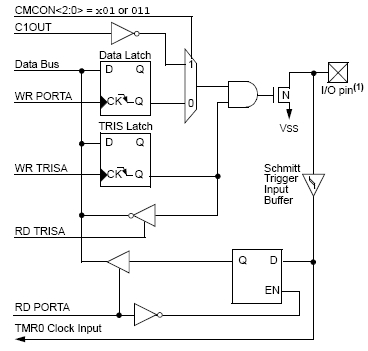

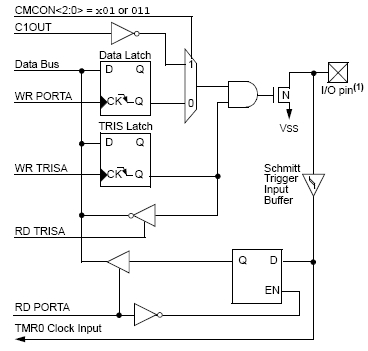

Dal punto di vista elettrico, il pin del PORTA può essere

schematizzato in questo modo:

|

Questo schema di principio è valido per i PORTA 0, 1, 2, 3, 5.

Un elemento del bus dati (a 8 bit) è collegato al latch dei dati

(in uscita - Data Latch), al registro del TRIS (TRIS Latch) e,

attraverso un buffer tree-state, al latch di ingresso.

Una coppia di MOSFET P e N pilota il pin quando è

programmato come uscita.

Se viene programmato come ingresso attraverso il TRIS (Tree-state

Register), il buffer di uscita viene disabilitato e il pin è

collegato solamente ad un buffer TTL e ad un ingresso del modulo AD.

Se viene selezionata la modalità analogica (attraverso ADCON1),

il buffer TTL è bloccato e il segnale del pin perviene solamente al

modulo AD (una lettura del PORTA riporterà 0 per i pin configurati

come analogici).

|

|

Leggermente diversa è la struttura di RA4.

Se resta identico il sistema dei registri di latch, TRIS e dati,

una differenza sensibile è il buffer di uscita: si tratta di un open

drain su un MOSFET a canale N, quindi collegato con il source

alla Vss.

Dato che l' ingresso può essere diretto al TIMER0, il gate TTL

viene sostituito da uno Schmitt Trigger, con funzione di

"ripulitura" del segnale.

Altra differenza riguarda il fatto che questo pin non fa parte

degli ingressi AD, ma può, invece, diventare uscita del

comparatore 1 (C1OUT). La selezione viene effettuata con un bit del

registro CMCON.

Una descrizione più dettagliata della struttura dei port è

disponibile qui. |

La tabella seguente riporta il quadro completo di queste

possibilità. Da notare che, a seconda della funzione programmata, possono

esserci disponibili diversi tipi di buffer collegato al pin: ad esempio, il

pin relativo al TIMER0 è uno Schmitt Trigger (allo scopo di squadrare

al meglio il segnale); negli altri pin il buffer di ingresso è adeguato ai

livelli logici TTL.

Le uscite digitali sono delle coppie CMOS, escluso RA4 che è un open drain.

|

Pin

|

Funzione

|

TRIS

|

I/O

|

Tipo

|

Descrizione

|

|

RA0

AN0

C1-

|

RA0

|

0

|

O

|

DIG

|

LATA<0> uscita

digitale

|

|

1

|

I

|

TTL

|

PORTA<0> ingresso

digitale

|

|

AN0

|

1

|

I

|

ANA

|

ingresso analogico

canale 0

ingresso comparatore C1-

|

|

RA1

AN1

C2-

|

RA1

|

0

|

O

|

DIG

|

LATA<1>

uscita digitale

|

|

1

|

I

|

TTL

|

PORTA<1>

ingresso digitale

|

|

AN1

|

1

|

I

|

ANA

|

ingresso

analogico canale 1

ingresso comparatore C2-

|

|

RA2

AN2

Vref-

C2+

CVref

|

RA2

|

0

|

O

|

DIG

|

LATA<2>

uscita digitale

|

|

1

|

I

|

TTL

|

PORTA<2>

ingresso digitale

|

|

AN2

|

1

|

I

|

ANA

|

ingresso

analogico canale 2

ingresso comparatore C2+

|

|

Vref-

|

1

|

I

|

ANA

|

ingresso tensione di

riferimento (low) del convertitore A/D

|

|

CVref

|

-

|

O

|

ANA

|

uscita tensione di

riferimento dei comparatori

|

|

RA2

AN2

Vref+

C1+

|

RA3

|

0

|

O

|

DIG

|

LATA<3>

uscita digitale

|

|

1

|

I

|

TTL

|

PORTA<3>

ingresso digitale

|

|

AN3

|

1

|

I

|

ANA

|

ingresso

analogico canale 3

ingresso comparatore C1+

|

|

Vref+

|

1

|

I

|

ANA

|

ingresso

tensione di riferimento (high) del convertitore A/D

|

|

RA4

C1out

T0CKI

|

RA4

|

0

|

O

|

DIG

|

LATA<4>

uscita digitale

|

|

1

|

I

|

ST

|

PORTA<4> ingresso

digitale

|

|

T0CKI

|

1

|

I

|

ST

|

ingresso clock esterno

Timer 0

|

|

C1out

|

0

|

O

|

DIG

|

uscita compratore C1

|

|

RA5

AN4

!SS

HLVDIN

C2OUT

|

RA5

|

0

|

O

|

DIG

|

LATA<5>

uscita digitale

|

|

1

|

I

|

TTL

|

PORTA<5>

uscita digitale

|

|

AN4

|

1

|

I

|

ANA

|

ingresso

analogico canale 4

|

|

!SS

|

1

|

I

|

TTL

|

Slave select dell' MSSP

|

|

HLVDIN

|

1

|

I

|

ANA

|

ingresso rivelatore

variazione di tensione

|

|

C2out

|

0

|

O

|

DIG

|

uscita

compratore C2

|

|

OSC2

CLKO

RA6

|

RA6

|

0

|

O

|

DIG

|

LATA<6>

uscita digitale

|

disponibile

se selezionato

RCIO, ECIO, INTIO2

|

|

1

|

I

|

TTL

|

PORTA<6>

uscita digitale

|

|

OSC2

|

-

|

O

|

ANA

|

feedback out dell'

oscillatore (modi LP,XT.HS)

|

|

CLKO

|

-

|

O

|

DIG

|

uscita clock /4 (modi

RC, INTIO1, EC)

|

|

OSC1

CLKI

RA7

|

RA7

|

0

|

O

|

DIG

|

LATA<7>

uscita digitale

|

disponibile se

selezionato

INTIO2

|

|

1

|

I

|

TTL

|

PORTA<7>

uscita digitale

|

|

OSC1

|

-

|

I

|

ANA

|

ingresso oscillatore

(modi LP, XT, HS)

|

|

CLKI

|

-

|

I

|

ANA

|

ingresso clock (modi EC)

|

- = non dipende dal registro TRIS

DIG = uscita digitale

TTL = buffer di ingresso livello logico

ST = ingresso con trigger di schmitt

ANA = ingresso (uscita) analogico

I pin di PORT A

posso quindi

assumere le seguenti funzioni :

RA7:0)

Si

tratta della funzione generica di ingresso/uscita (GPIO General Purpose

IO), dove la direzione è stabilita dal solito registro TRIS. PORTA

è il registro dello stato della porta (in lettura e scrittura), mentre

LATA

è il registro del latch della porta in uscita.

Solitamente PORTA non è presente al completo con tutti gli 8

bit, ma sono disponibili solo 6 pin, da RA0 a RA5.

I restanti due pin sono derivabili da quelli dell' oscillatore

esterno (OSC1 e OSC2) nel caso in cui esso non venga usato (modi INTIO),

dove possono dare origine a RA6 e RA7.

Va ricordato anche che RA4 , come uscita digitale, è un open drain,

quindi può comandare carichi appesi alla Vdd (sink current), ma non

verso la Vss (source current), caso in cui va utilizzato con un pull-up

esterno.

ADC (AN 4:0)

La

funzione ADC (Analog to Digital Converter) coinvolge i pin RA3:0

e RA5. Da osservare che RA4 non può assumere funzioni analogiche

L' operatività dipende

dal registro ADCON1 (ved.

Modulo AD).

Ad esempio, per programmare tutti i pin come GPIO, escludendo le

funzioni analogiche, occorrono le seguenti due righe :

movlw 0x07

movwf

ADCON1

ATTENZIONE:

Dopo

il reset del Power-On, i pin RA3:0 e RA5 sono configurati per default

come ingressi analogici, mentre RA4 è un ingresso digitale. Questo

rende indispensabile, nelle prime fasi di inizializzazione dell'

hardware, dedicare una parte alla corretta definizione delle funzioni di

questi pin.

|

Della funzione analogica fanno parte anche gli ingressi

+Vref e -Vref, abilitabili sui pin indicati.

Il foglio dati, in relazione al modulo AD, riporta una tabella delle

funzioni di ADCON1, in cui i bit PCFG3:0 permettono di

selezionare quali port dedicare all' analogica. Si può osservare che la

tabella ha contenuto "triangolare", il che permette di assegnare

alla funzione analogica uno o più pin in sequenza.

Da osservare che In alcuni processori la funzione analogica

può essere attribuita anche a pin di PORT B o PORT E.

Siccome anche qui, per default al Power On ai pin viene assegnata la

funzione analogica, occorrerà agire sulla configurazione o siui registri

per poter utilizzare questi pin come IO.

Altri dettagli sono disponibili nelle pagine relative al modulo AD.

-

Comparatori

analogici

La

famiglia PIC18F432x mette a disposizione due compratori analogici

i cui pin di ingresso /uscita possono essere multiplexati sui pin di

PORTA

. Le funzioni

di comparazione sono controllate da appositi registri

(COMCON<2:0>) attraverso cui possono essere configurate e

abilitate/disabilitate.

I pin attribuiti ai comparatori come ingressi o uscite non sono

impiagabili come GPIO o peraltre funzioni speciali.

Per default i

comparatori sono disattivato dopo un POR, ma, in ogni caso, se le

funzioni di comparazione non sono usate, è opportuno disabiltarle nelle

prime righe del programma.

Altri dettagli sono disponibili nelle pagine relative ai comparatori.

-

Modulo Generatore della tensione di riferimento

Pensato principalmente per l' uso con i comparatori, questo modulo può

essere impiagato anche per scopi diversi, avendo la possibilità di

collegare la sua uscita con il pin RA2 (che, in queste condizioni, non

può avere alcun altro impiego).

Altri dettagli sono

disponibili nelle pagine relative ai comparatori.

-

Ingresso modulo HLVD

Il modulo rivelatore di variazione di tensione può avere un

ingresso esterno attraverso RA4.

Altri dettagli sono

disponibili nelle pagine relative al modulo HLVD.

-

Ingresso salve select dell' MSSP

Il port RA5 è l' ingresso di slave select del modulo MSSP.

Altri dettagli sono

disponibili nelle pagine relative al modulo MSSP

-

Ingresso del Timer0

Il port RA4 può essere utilizzato come ingresso (Schmitt trigger) per

il Timer0.

Altri dettagli sono

disponibili nelle pagine relative al TIMER0

Inoltre, come detto, i pin "extra" RA6 e RA7 sono

derivabili come GPIO o come ingressi/uscite del modulo oscillatore a seconda

di come questo è configurato. La scelta della modalità dell' oscillatore

viene fatta con le righe di configurazione iniziale del sorgente e non è

mutabile durante l' esecuzione del programma.

A seconda della modalità scelta, RA6 e RA7 possono essere:

| Funzione |

RA6 |

RA7 |

| oscillatore XT, HS, LP |

oscout |

oscin |

| oscillatore esterno |

EC |

F/4

|

oscin |

| ECIO |

GPIO

|

oscin |

| oscillatore RC |

RC |

F/4 |

oscin |

| RCIO |

GPIO |

oscin |

| oscillatore interno |

INTIO1 |

F/4 |

GPIO |

| INTIO2 |

GPIO |

GPIO |

Maggiori dettagli sono reperibili nelle pagine

dedicate ai modi dell' oscillatore.

I registri associati a PORTA

I registri associati all' uso di PORT A

sono i seguenti :

|

Nome

|

bit 7

|

bit 6

|

bit 5

|

bit 4

|

bit 3

|

bit 2

|

bit 1

|

bit 0

|

|

PORTA

|

RA7*

|

RA6*

|

RA5

|

RA4

|

RA3

|

RA2

|

RA1

|

RA0

|

|

LATA

|

Data latch

|

|

TRISA

|

Data direction

- 1 = input / 0 = output

|

|

CMCON

|

|

|

|

|

|

CM2

|

CM1

|

CM0

|

|

CVRCON

|

CVREN

|

CVROE

|

|

|

|

|

|

|

|

ADCON1

|

|

|

|

|

PCFG3

|

PCFG2

|

PCFG1

|

PCFG0

|

|

CONFIG1H

|

|

|

|

|

FOSC3

|

FOSC2

|

FOSC1

|

FOSC0

|

I bit non indicati non sono usati dalla gestione di PORTB. I

bit indicati con * sono eventualmente disponibili solo se si è configurata

una modalità di oscillatore interno.

Situazione al POR

Al POR :

A

= 11111111, ovvero la

direzione generale dei pin è come ingresso.

PORTA

e LATA

hanno contenuto indeterminato.

In ADCON1

il valore dei bit PCFG<2:0>

è 1, quindi AN5:0 programmati come input analogici

Per quanto riguarda i registri di controllo dell' interrupt,

al POR tutti gli Interrupt sono disabilitati

Nei registri di configurazione, per default:

Per quanto riguarda le funzioni speciali (ADC, Interrupt INT

e PORTB Change, CCP, ICSP , ICD e LVP) consultare i capitoli relativi.

Si può riassumere la situazione del POR in questo modo :

-

I pin RA3:0 e RA5 sono configurati come ingressi

analogici. La funzione può essere modificata con ADCON1.

Il pin RA4 è configurato come ingresso digitale. Per ottenere un

default di ingressi digitali occorre agire su PBADEN in fase di

configurazione

-

RA6 è disponibile come ingresso digitale, essendo

configurato di default un oscillatore RC esterno con input su RA7. Una

diversa configurazione dell' oscillatore richiede l' opportuna linea di

comando nel sorgente.

-

Nessun interrupt dipende direttamente da PORTA

.

-

Nessuna funzione speciale è abilitata per default sul PORT A

Anche i comparatori analogici sono disabilitati. Comunque

gli esempi Microchip di inizializzazione del PORTA

contengono una azione su CMCON se in comparatori non sono richiesti.

Inizializzazione di PORTA

Una sequenza di inizializzazione come GPIO digitale può

essere questa :

;

Inizializza

PORT A

clrf PORTA

; clear PORTA latch

;clrf LATA

; metodo alternativo per il clear

movlw 0x0F

; tutti i pin come GPIO

movwf ADCON1

movlw 0x07

; disabilita i comparatori (se necessario)

movwf CMCON

movlw b'11001111'

; set RA7:6 e RA3:0 come input

movwf TRISA

; e RA5:4 come out |

In effetti le possibilità di PORTA sono molto maggiori,

essendo legata anche ad altre funzioni; l' inizializzazione delle funzioni

speciali è trattata in dettaglio nei capitoli relativi.

NOTE:

-

Per default al POR i registri che

interessano PORTA assumono valori ben definiti, che possono non

essere quelli richiesti dal programma

-

RA6 e RA7 sono disponibili solo in

conseguenza di specifiche scelte del modo dell' oscillatore.

Queste scelte sono effettuate in fase di configurazione del chip

e non sono modificabili durante il funzionamento

-

La funzione HLVDIN è trattata in un

apposito capitolo

-

La funzione !SS riguarda l' attivazione e

la configurazione del modulo MSSP.

-

Le funzioni speciali sono prioritarie

rispetto a quelle di GPIO, per cui, ad esempio, un pin

programmato come uscita della tensione di riferimento o entrata

analogica non sarà utilizzabile come I/O generico.

I pin impostati come ingressi analogici, letti nel registro

PORTA rendono 0.

-

Occorre verificare con cura il valore da

attribuire a TRIS per avere disponibile la funzione voluta : ad

esempio, il bit di TRIS funge da enable/disable per le

uscite dei comparatori

-

RA4 come uscita digitale è un open drain,

quindi può pilotare solo carichi appesi alla Vdd (current sink).

Questo vale anche quando viene usato come uscita del Comparatore

1

L' errata inizializzazione sia del TRIS che dei

registri ADCON1, CMCON e CVRCON impedisce l' uso dei pin nel modo

voluto.

|

|

|

|

Copyright © afg. Tutti i diritti riservati.

Aggiornato il 09/12/10.

|