Sospendiamo momentaneamente l' analisi dei modi di

indirizzamento per ritornare al foglio dati, che a pag.62 fornisce una

descrizione dei registri SFR.

Gli SFR

Gli Special Function Registers o

SFR

sono quelle locazioni in memoria dati che contengono quanto necessario per la

gestione delle periferiche integrate,

per lo stack, le tabelle, gli interrupt, ecc.

Se

nei PIC16 gli SFR erano spalmati su più banchi, costringendo il

programmatore ad inseguirli con gli switch RP, negli enhanced si trovano

tutti nella parte più alta della memoria, nel banco 15.

Questo

è già un vantaggio, in quanto non è più necessario uno switch di banco per

passare da un SFR all' altro.

Inoltre la metà del banco 15 che li contiene è accessibile, come abbiamo visto prima, in modo semplificato con l' Access RAM, ovvero gli SFR sono

raggiungibili senza operazioni particolari da qualunque banco di memoria si

stia lavorando.

Gli

SFR si possono suddividere in due gruppi:

-

quelli

associati al "core" del processore (ALU, RESET, Interrupt)

-

quelli

associati alle periferiche integrate (port, AD, Timers, ecc.)

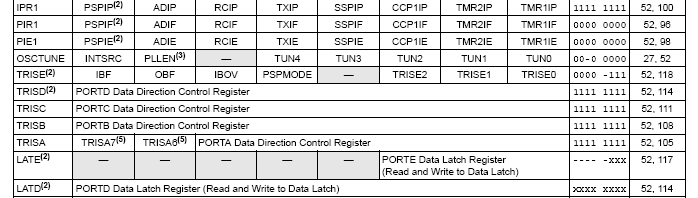

La pagina 62 del foglio dati riporta una

tabella in cui sono elencati tutti gli SFR con il loro indirizzo assoluto e

che è inutile riportare qui.

Piuttosto è utile evidenziare alcuni

punti:

-

Alcuni SFR non sono registri realmente

presenti in memoria, ad esempio quelli dell' indirizzamento indiretto (INDF)

-

Non

tutte le locazioni di memoria del banco 15 sono occupate da SFR; questo

dipende dalle caratteristiche dei chip e va verificato sul relativo foglio

dati

-

Così pure non tutti i registri sono a

8 bit completi. In ogni caso, i registri non impegnati o i bit non

utilizzati rendono, come solito, 0 in lettura e se scritti il dato va

perso.

Le tavole 5.2 a pagina 63, 64, 65

dettagliano ogni singolo registro con:

e, in più, una utile raccolta dello stato

che assumono questi bit al momento del Power On Reset (POR) o del BOR (Brown

Out Reset).

Si potrà osservare che:

-

alcuni bit vengono posti a 1, altri a zero.

-

altri non vengono modificati dalla loro situazione precedente, ovvero se il

chip è attivo e questi registri sono stati inizializzati, POR o BOR non ne

modificano il valore.

-

Per altri ancora, il valore assunto dopo questi eventi è casuale, non

definibile a priori.

Un' ultima colonna riporta un utile indice

delle pagine in cui i registri sono descritti.

Per meglio esemplificare prendiamo un

tratto della tabella a pagina 65.

Vediamone alcuni :

IPIR1: E' composto da 8

bit, tutti attivi e i cui nomi sono elencati. Al POR/BOR tutti i bit sono

portati a 1

PIR1 : E' pure composto da 8 bit che al POR/BOR sono portati a 0

(disabilitando i relativi interrupt periferici)

OSCTUNE : il bit 6 non è implementato e tutti i bit sono a 0 al POR/BOR

LATE: soltanto i primi tre bit sono utilizzati e il loro valore al

POR/BOR è indeterminato.

LATD: tutti i bit sono validi e anche in questo caso il loro valore

al POR/BOR è indeterminato

E

così via.

NOTE:

- I nomi dei registri e dei loro bit sono quelli che si ritrovano

come label nel files .INI relativi a ciascun processore.

- Salvo poche eccezioni, i nomi sono gli stessi per tutti i

chip.

- Quindi, maggior ragione ancora per evitare tassativamente l'

uso di indirizzi assoluti, sempre sostituiti dalle

corrispondenti label.

- Ovviamente non tutti i chip, non avendo lo stesso set di

periferiche, non hanno gli stessi SFR e/o gli stessi bit, anche

all' interno della stessa famiglia. Ad esempio, nel caso visto

prima, il LATE, che dipende dal PORTE, è disponibile solo sui PIC

a 40 e più pin, ma non sui 28 pin.

Come al solito, la lettura del foglio dati serve a chiarire anche

quali SFR sono disponibili per quel determinato componente. |

Vedremo più avanti nel dettaglio i vari SFR.