Il

ciclo delle istruzioni

Può essere di una certa importanza il conoscere quale sia il

meccanismo di svolgimento di una istruzione.

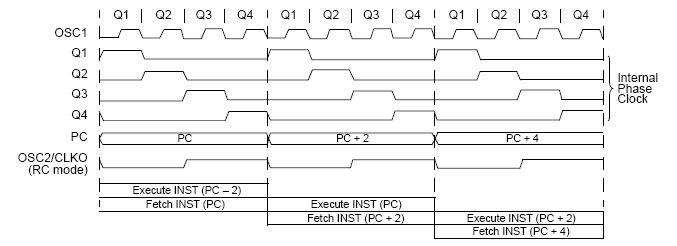

Il clock in ingresso nel microprocessore, sia che venga da un

oscillatore esterno ce da uno interno, viene diviso per quattro e genera quattro

sotto clock in quadratura, non sovrapposti, denominati Q1, Q2, Q3 e Q4.

Internamente, il program counter è incrementato ad ogni

Q1.

Il codice dell' istruzione viene letto dalla cella della memoria programma in

cui è conservato e viene latchata in un registro provvisorio detto Instruction

Register (IR). L' istruzione è decodificata ed eseguita tra Q1 e Q4.

Le fasi relative ad una istruzione si sovrappongono con quelle

dell' istruzione seguente, ottenendo una maggiore efficienza e rapidità di

esecuzione.

Dal diagramma qui sopra si può vedere meglio il fatto che le

varie fasi sono "pipelined", eseguite in parallelo.

Per cui fetch richiede un ciclo e decodifica e esecuzione richiedono un altro

ciclo, ma, essendo sovrapposti quelli di una istruzione con quelli della

successiva, si ottiene come risultato che la maggior parte delle istruzioni

necessita di un solo ciclo per essere eseguita.

Il ciclo comincia in Q1 con la presa in carico del codice dell'

istruzione nel registro IR. Questa istruzione è decodificata ed eseguita

durante Q2, Q3 e Q4. La memoria dati è letta in Q2 e scritta in Q4.

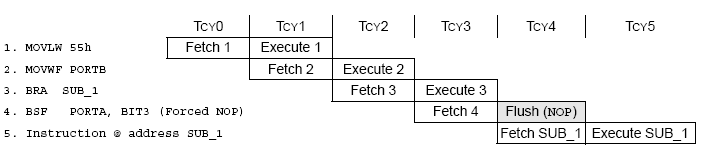

Ad

esempio, una breve sequenza di istruzioni si svolge in questo modo:

Questo

rende conto del fatto che il ciclo di istruzione è 1/4 del clock primario.

Per

cui ci sarà una relazione del tipo:

Ciclo Istruzione =

Clock Principale / 4

e questo permette di calcolare con

esattezza la durata di un certo insieme di istruzioni e creare riferimenti di

tempo.

Ecco un a tabella per avere una idea del rapporto tra

clock e durata dell' istruzione (a ciclo singolo).

| Clock |

Ciclo

istruzione |

|

Clock |

Ciclo

istruzione |

| 32 kHz |

125 us |

|

16 MHz |

250 ns |

| 1 MHz |

4 us |

|

20 Mhz |

200 ns |

| 4 MHz |

1 us |

|

24 MHz |

150 ns |

| 8 MHz |

500 ns |

|

32 MHz |

125 ns |

| 10 MHz |

400 ns |

|

40 MHz |

100 ns |

| 12 MHz |

300 ns |

|

48 Mhz |

83,3 ns |

Istruzioni che impiegano più cicli avranno un impegno di tempo

pari al numero dei cicli.

Ad esempio, un branch condizionato, del

genere BTFSS, a 40 Mhz di clock impiega:

-

se non eseguito: 1 ciclo, ovvero 100 ns

-

se eseguito sull' istruzione successiva a 2 bytes: 2 cicli,

ovvero 200 ns

-

se eseguito sull' istruzione successiva a 4 bytes: 3 cicli,

ovvero 300 ns

NOTE:

Va notato che non tutte le istruzioni si risolvono in un solo

ciclo.

Ad esempio branch e jump richiedono più cicli.

Così pure i

salti condizionati, se eseguiti, richiedono due o tre cicli.

|