|

La Memoria

Continuando il nostro tour nel foglio dati del PIC18F2321, incontriamo una

descrizione della memoria.

|

Trattandosi di un RISC con struttura Harvard,

l' area di memoria è divisa in due parti:

-

la MEMORIA

PROGRAMMA (Program Memory), in tecnologia Flash

-

la MEMORIA

DATA (Data Memory), in tecnologia RAM CMOS

Come per i PIC della famiglia 16, anche i 18F utilizzano la struttura

Harvard,

dove la memoria programma e la memoria dati sono dipendenti da due bus diversi.

|

La Memoria Programma è l' area d o ve vengono

posti

i codici

operativi (opcodes) e i vari elementi del programma.

Si tratta di memoria del

tipo FLASH, non volatile,

ovvero che conserva il dato conten uto anche se viene a mancare la tensione di

alimentazione. Inoltre è scrivibile e cancellabile elettricamente, con la possibilità di

operare sull' area dall' interno del programma stesso,

con un evidente ampliamento delle possibili gestioni automatiche del firmware (update, auto apprendimento, bootloader, ecc).

La Memoria Dati tipicamente è una RAM statica, volatile,

ovvero che perde i dati contenuti al mancare della tensione di alimentazione.

Questa RAM contiene

una serie di registri di uso generico,

detti GPR -

General Purpose Registers,

cioè locazioni ampie un byte (8 bit) il cui contenuto può essere scritto e

letto attraverso le istruzioni del programma e dedicate a contenere le variabili

utilizzate; inoltre,

nell' area RAM si trovano i

registri di controllo delle funzioni del processore e dell' I/O integrato,

detti SFR -

Special Function

Registers.

MEMORIA PROGRAMMA

Pur mantenendo una struttura del tutto simile, le differenze tra i

PIC 16 e i 18 sono sensibili.

|

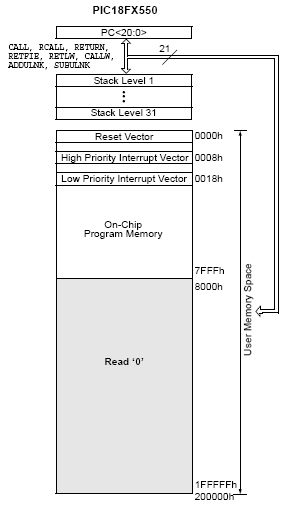

A lato è riportato lo schema di memoria programma di un processore

della famiglia 18Fx550. La Memoria Programma comprende

- un Program Counter a 21 bit, con cui si arriva teoricamente ad indirizzare direttamente un' area di 2MB,

rispetto ai 2kB della serie 16.

- Lo STACK, che nei 16F ha una profondità di 8 livelli, qui raggiunge

31 livelli, con parole da 21 bit, permettendo un annidamento molto più

complesso delle chiamate a subroutine; inoltre lo stack può essere

manipolato da istruzioni specifiche. Questo consente una maggiore efficienza

dei compilatori dei linguaggi ad alto livello.

- L' area della Memoria Programma vera e propria è costituita da

celle a 16 bit ed inizia con il vettore di reset, che è sempre a 0x00,

mentre quello di interrupt si differenzia in due entry point, uno a 0x08 e

l' altro a 0x18, il primo con una maggior priorità sul secondo.

Le istruzioni PIC 18F sono a 16 bit, escluse 4 che sono a 32 e quindi

occupano 2 word consecutive.

Lo schema a lato esemplifica la Progam Memory della serie 18Fx550, che

termina a 7FFFh, ovvero 32kB. Altri processori dispongono di tagli

diversi, da 4 a 128 kbytes (2 - 64 kwords).

L' area di memoria non

utilizzata, se letta, riporta il valore 0. Scrivendola, non succede nulla. |

Nei

PIC18 la memoria programma indirizzabile è ampia 2 Mbytes ed è accessibile

integralmente senza modificare il PCLATH, ovvero non esistono più paginazioni

della memoria programma: si tratta di una sola, unica pagina,

qualunque sia la sua dimensione.

Le istruzioni del set enhanced dispongono di un

meccanismo di indirizzamento adeguato.

Per tutti i PIC18, la memoria programma, a seconda del modello, va da 4 a 128

Kbytes.

In relazione all' estensione di questa memoria, va osservato che l' indicazione in k

fa riferimento ai byte;

considerando che la maggior parte delle istruzioni dei PIC18F è a 16 bit, il

quantitativo della memoria va diviso per due, ovvero 32k potranno ospitare 16k

istruzioni a un word (tenendo anche presente che esistono alcune istruzioni che occupano 2

word, ovvero 4 bytes). In conseguenza di questo fatto, nelle caratteristiche dei chip, il costruttore aggiunge anche l’

indicazione di un “Program Memory Kwords”, pari alla metà di quanto

indicato nel parametro “Program Memory Kbytes”.

Questa considerazione è necessaria per avere

una corretta idea della capacità in istruzioni.

Si deve anche

notare che alcuni PIC hanno la possibilità di accedere e indirizzare memoria

esterna come se fosse integrata; solitamente si tratta di dispositivi a 80 pin.

Non esistendo una

frammentazione in pagine, come accadeva nei 16F, non occorre più tenere

sotto controllo questo punto, il che solleva il morale del

programmatore, spesso alterato dalla lotta con gli switches del PCLATH quando

occorre cacciare grossi programmi nei

piccoli PIC.

La realizzazione una unica pagina, infatti, rende

superflui i non semplici meccanismi che è necessario, invece, implementare nei

mid-range quando il programma occupa più di una pagina.

La Memoria Programma nella famiglia PIC18F4321

Come abbiamo visto nelle pagine iniziali che descrivono i membri

della famiglia 18F4321, i chip siglati 18Fx2xx hanno 2 K di Flash, mentre quelli

siglati 18Fx3xx ne hanno 4 K.

A parte questa differenza, il resto della suddivisone a

blocchi è identico.

|