|

Torniamo all' analisi del nostro convertitore AD di tipo SAR.

Sequenza della conversione SAR

Dal punto di vista elettrico, il funzionamento è questo:

- La tensione di ingresso Vin viene catturata da un sample

& hold; questo è necessario in quanto la conversione non è

istantanea,

ma impiega un certo tempo: se durante questo tempo la tensione varia, la misura non

sarebbe significativa.

Quindi, attraverso il sample&hold, il convertitore SAR

"fotografa" un determinato istante di tensione ed opera su questa

immagine.

Questo è un elemento importante da ricordare.

- L' uscita del S&H è inviata ad un comparatore

che ha come altro ingresso la tensione fornita da un convertitore digitale-analogico

(DAC).

Il DAC è un circuito che riceve come ingresso un certo numero di bit

digitali e rende in uscita una serie di gradini di tensione proporzionali al

dato binario di ingresso (è l' opposto dell'ADC). Si tratta dell'

equivalente dei pesi della bilancia prima esemplificata: associando

ai pesi campione delle cifre binarie si può esprimere il peso dell'oggetto

in forma digitale.

- L' ingresso del DAC è controllato da un registro a N bit

che fornisce la serie dei valori digitali. Quanto maggiore è il numero dei

bit disponibili, tanto maggiore sarà la definizione dei gradini di tensione

in uscita dal convertitore AD.

- Lo scorrere dei dati nel registro è regolato da un clock, che fa avanzare

il conteggio.

- L' avviamento della conversione è dato da un segnale di Start of

Conversion, che avvia il processo. Questo segnale è generato attivando un

bit in un registro di controllo, dopo il tempo di acquisizione del S&H

- Dopo il segnale di avvio della conversione, il registro SAR è

inizializzato al valore "100...0", ovvero con il bit più

significativo (MSb, ovvero il bit N-1) a 1 ed i restanti bit a 0. Questo

punto equivale a metà del range dinamico del convertitore e, al primo colpo

di clock, le sue uscite binarie comandano il DAC, fornendo un primo

livello analogico, pari a metà della tensione di riferimento e che il

comparatore confronta con il valore da misurare. Si possono verificare due e

casi:

- Vin è maggiore di Vdac: l'uscita del comparatore va al valore alto

(1 logico) e il bit MSb del registro rimane ad '1'.

- Vin è minore di Vdac : l'uscita del comparatore va bassa ( 0 logico ) e

il bit MSb del registro viene settato a "0".

- Al successivo colpo di clock si confronta la nuova tensione di uscita del

DAC (dovuta all'aggiornamento del registro) con la tensione di ingresso.

Qui si rende evidente la necessità che questa tensione resti stabile per

tutto il tempo di conversione e quindi la necessità del S&H.

Se la tensione di ingresso è maggiore o uguale, il bit N-2 è a 1 e si pone

il bit N-3 a '1'. Se invece la tensione è minore, si porta il bit N-2 a 0 e

il bit N-3 a 1.

- Al colpo successivo di clock un'

altra comparazione e' avviata e il risultato viene trattato come sopra. In

sostanza, la tensione da misurare è comparata con una frazione sempre più

piccola della tensione di riferimento e ad ogni step il corrispondente bit

del registro SAR viene adeguato al risultato della comparazione.

Si ha così

la serie di "approssimazioni successive" tra l' uscita del DAC e

la tensione da misurare: quanto maggiore è il numero di bit N tanto

migliore sarà l' approssimazione tra il valore analogico e quello

digitalizzato.

- Questa sequenza di operazioni finisce, quindi, quando il numero di colpi

di clock ha raggiunto la comparazione relativa al bit meno

significativo (LSb).

ne deriva che la conversione richiede, al minimo, un numero di impulsi

di clock pari al numero dei bit da convertire.

- L' evento viene indicato da un flag EOC (End Of Conversion) e il

gruppo di N bit collezionati nel registro costituisce il risultato binario

(digitale) della conversione

|

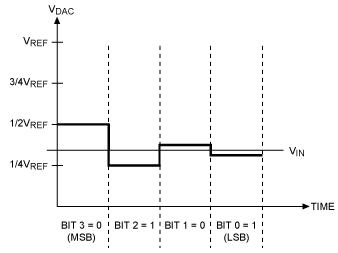

Il grafico a lato mostra un esempio di una conversione di 4

bit.

L'asse y (e la linea grassetto nella figura) rappresenta la

tensione in uscita dal DAC, che varia a seconda del contenuto del

registro SAR. Sull' asse x sono riportati i vari livelli di tensione

possibili.

Nell'esempio, il primo confronto mostra che VIN < VDAC.

Così, il bit 3 è impostato su 0. Il DAC viene quindi impostata su

0100bin e viene eseguito il secondo confronto.

Con VIN > VDAC, il bit 2 resta a 1. Il DAC viene quindi impostata

su 0110bin e viene eseguito il terzo confronto.

Il bit 1 è posto a 0 e il DAC viene quindi impostato su 0101bin

per il confronto finale.

Infine, bit 0 resta a 1 perché VIN > VDAC.

|

Aggiornati tutti i bit, si genera l'EOC e il processore potrà prelevare il

risultato della conversione, ovvero 1010.

Un SAR ADC richiede quindi:

-

- una sorgente di ingresso Vin.

- una sorgente della tensione di riferimento Vref

con cui comparare l' ingresso.

- un DAC per la conversione ad approssimazioni successive .

- un singolo comparatore che confronta l' uscita del DAC con la

tensione di ingresso.

- un registro (SAR) per raccogliere i risultati delle comparazioni

successive

Inoltre sarà necessario un sample & hold all' ingresso per mantenere

stabile la tensione Vin durante la conversione.

I due componenti critici di un ADC SAR sono il comparatore e il DAC. I

requisiti sono velocità e precisione.

Poiché il registro SAR è di N bit, ci vogliono N colpi di clock per aggiornare

tutto il registro SAR. Ovvero: il tempo necessario alla conversione è:

dove N è il numero di bit e Tclk è il periodo di

clock.

Quindi

| il tempo necessario alla conversione dell' AD SAR non dipende dal

valore della tensione in ingresso, ma dipende

solo dal

numero dei bit e dalla frequenza del clock |

Ovviamente:

- maggiore è il numero di bit del risultato, maggiore sarà il tempo di

conversione (a parità di clock)

- maggiore sarà la frequenza del clock, minore sarà il tempo di

conversione (a parità di risoluzione)

Inoltre, va considerato che

- minore è la

velocità del clock, minore sarà l' energia richiesta dal dispositivo

e questa

caratteristica è interessante per le implementazioni a basso consumo.

Peraltro il clock, se non può essere superiore ad un massimo,

non può essere inferiore ad un minimo, in quanto va ricordato che la

tensione di ingresso è fornita dal condensatore del S&H ed occorre

completare la conversione prima che il valore della tensione campionata si

deteriori per la scarica del condensatore.

Ad esempio, nei PIC a 8 bit il clock del modulo ADC in genere può variare tra

50 e 625 kHz.

Un bilanciamento tra risoluzione e clock potrà

essere necessario in applicazioni che necessitano di prestazione oppure di basso

consumo.

|

La velocità della conversione, in

realtà dipende anche da altri fattori, ad esempio:

-

Il tempo acquisizione del

S&H, che è basato sulla carica di un piccolo condensatore (capacità di

Sample)

-

la velocità del comparatore e

della logica di controllo del registro

-

Il tempo di assestamento del

circuito nel suo insieme

-

I tempi di risposta del processore nella

gestione dell' ADC

In sostanza, per avere una idea del

massimo numero di conversioni possibili in una unità di tempo dobbiamo tenere

conto delle caratteristiche operative del convertitore, ma anche del processore a cui è

connesso.

|

Dal punto di vista operativo, questo sistema richiede che il processore fornisca il segnale di avvio della

conversione e ne prelevi il risultato al seguito dell' azionamento del flag

EOC.

E, inoltre, che sia fornito un clock al convertitore.

Nei sistemi embedded, dove il modulo ADC è integrato nel microcontroller,

alcuni registri contengono i bit di controllo del convertitore e del suo clock,

mentre i risultati della conversione sono accessibili direttamente sul bus dati.

ADC esterni potranno richiedere clock e tensione di riferimento esterne oppure

potranno disporne internamente e colloquieranno con il processore attraverso

interfacce parallele o seriali del genere I2C e SPI.

Vediamo ora qualche altra considerazione su alcuni parametri dell' ADC.

|