|

I pin di ingresso dei circuiti digitali, compresi i microcontroller,

presentano solitamente una impedenza abbastanza alta, assieme alla possibilità di

operare su segnali ad elevata frequenza.

Questo significa che, se sono lasciati flottanti, ovvero senza alcun

riferimento di tensione, sono soggetti a captare qualsiasi disturbo

elettromagnetico o elettrostatico e quindi a commutare le loro uscite in modo

casuale. E si definisce floating - flottante un pin di ingresso a cui non

è collegato nulla.

Ne deriva la

necessità di porre sempre questi pin ad un adeguato livello alto o basso;

condizioni intermedie al di fuori dei margini di sicurezza portano a stati di incertezza che possono dare origine a

commutazioni indesiderate e mal funzionamento apparentemente difficile da

diagnosticare.

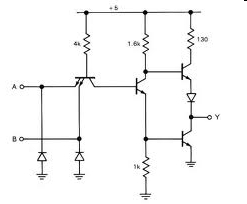

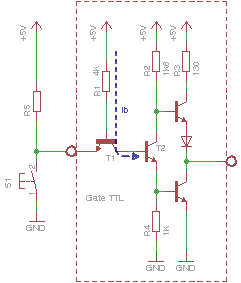

Vediamo ad esempio come è realizzato l' ingresso di una logica TTL

(Transistor Transitor Logic), una delle prime e principali famiglie, utilizzata ancora oggi.

|

Dal punto di vista costruttivo, un integrato TTL è realizzato con numerosi transistor bipolari.

A lato è schematizzato un blocco NAND: i due ingressi

A e B confluiscono in un transistor NPN ad emettitori

multipli.

Ad essi sono collegati esclusivamente dei diodi di protezione verso la

massa, ma non esiste alcuna resistenza o partitore all' interno dell'

integrato che

faccia assumere all' ingresso un livello determinato: sono floating.

E questo è corretto dato che il livello alto o basso dell'

ingresso dovrà essere stabilito dal circuito che lo precede. |

La logica NAND prevede la seguente tavola della verità:

| Ingressi |

Uscita |

| B |

A |

Y = A NAND

B |

| 0 |

0 |

1 |

| 0 |

1 |

1 |

| 1 |

0 |

1 |

| 1 |

1 |

0 |

Sappiamo che le cifre del sistema binario sono solo 2 : 0 e 1 e che esse

corrispondono, nel circuito eletytrico equivalente, a due livelli di tensione

ben determinati:

| 0 |

1 |

| basso |

alto |

| Gnd |

Vcc |

| Vss |

Vdd |

In effetti, per motivi costruttivi, si avrà questa equivalenza:

| 0 |

1 |

| "quasi" Gnd |

"quasi" Vcc |

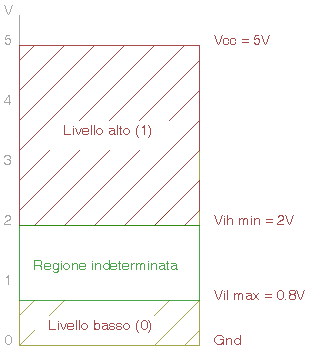

che, in forma grafica, possiamo rappresentare così:

|

- VIL — la massima tensione su un pin di ingresso che

verrà letta come un basso logico.

- VIH — la minima tensione su un pin di ingresso che

verrà letta come un alto logico.

- Forbidden region — la regione "indeterminata" tra il livello di

tensione VIL e VIH.

Tensioni di

ingresso in questo intervallo possono essere lette come basse o alte a

seconda di fattori casuali e costruttivi.

Come ingresso di un sistema

logico è ovvio che un livello produrrà un risultato piuttosto che il

livello opposto; quindi, è fondamentale che gli ingressi del circuito

logico siano ben determinati nel loro valore. |

Il campo di tensioni e livelli sopra indicato si definisce TTL level (Livello TTL).

I PORT dei PIC

Microchip, impostati come ingressi digitali, sono compatibili per la maggior parte con i livelli

TTL.

Dunque, per riassumere:

- il livello basso (0) è definito da una tensione di ingresso minore

di 0,8 volt

- il livello alto (1) è una tensione di ingresso maggiore

di 2.0 volt (alla tensione di alimentazione dell' integrato di 5 volt).

- Il campo di tensioni tra 0,8 e 2.0 è dichiarato come "Indefinito" o

illegale, ovvero, se applicato all' ingresso darà una uscita non

determinabile, casuale, e che, quindi, è una condizione da evitare assolutamente.

I livelli logici TTL costituiscono un punto di riferimento.

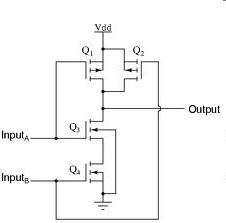

Analoga situazione per le logiche CMOS (Complementary MOS). Il livello

basso è < di 1.5 volt e quello alto è maggiore di 3.5 volt. Anche in

questo caso il campo di tensioni intermedio è illegale e, se applicato all'

ingresso darà una uscita non determinabile.

|

Dal punto di vista costruttivo, un ingresso CMOS è realizzato

integrando numerosi MOSFET P e N.

A lato è schematizzato un blocco NAND: si nota che i due ingressi

A e B confluiscono direttamente nei gate di due MOS a canale N.

Ad essi possono essere collegati dei diodi di protezione, sia verso la

Vss che verso la Vdd, ma anche qui non esiste alcuna resistenza o

partitore integrati che faccia assumere all' ingresso un livello

determinato: sono floating.

E questo è corretto dato che il livello alto o basso dell'

ingresso sarà stabilito dal circuito che lo precede. |

Va osservato che in questo caso l' impedenza degli ingressi A e B è

molto più elevata di quella della logica TTL, in quanto gli ingressi agiscono

direttamente sui gate di MOSFET che hanno impedenza di svariate decine di

megaohm. In entrambe le schematizzazioni della logica NAND, si deve

anche notare come gli ingressi, quando sono slegati da qualsiasi connessione,

non dispongono all' interno dell' integrato di alcun riferimento di tensione;

quindi, sono floating.

Se non applichiamo una condizione precisa all' ingresso,

la corrispondente uscita sarà determinata casualmente dalle caratteristiche

costruttive dell' integrato e, in modo rilevante, dai segnali elettromagnetici

e elettrostatici captati dal pin e dalle piste collegate, con le conseguenze

che si possono immaginare nella logica successiva. Facciamo un esempio

pratico di applicazione, che rappresenta un errore, purtroppo assai comune

negli schemi dei principianti:

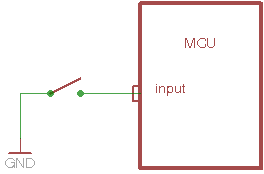

|

un ingresso digitale del microcontroller è dipendente dallo stato un contatto esterno

(interruttori, pulsanti, relè, ecc.) che chiude a massa. Se il

contatto è chiuso, il pin è collegato alla massa, quindi al livello

logico 0.

Ma fino a che il contatto è aperto, il pin si trova in una

situazione "flottante", senza essere agganciato ad alcuna tensione se

non, essenzialmente, quelle captate dalle connessioni tra il pin stesso e l'

interruttore.

|

Lasciare il circuito in queste condizioni è un errore molto grave,

in quanto sarà possibile, senza difficoltà, che campi elettrici

esterni, utilizzando la connessione tra il pin e il contatto come una

antenna, arrivino a indurre tensioni tali da far commutare il circuito

interno.

Quanto maggiore sarà la lunghezza delle connessioni, tanto maggiori

saranno le probabilità di captare un disturbo. Probabilità che diventa

certezza quando il circuito è inserito in ambienti elettricamente

rumorosi,

con presenza di relè, elettromagneti, trasformatori, motori, ecc., sopratutto in montaggi

disordinati. Altrettanto si deve dire per i pin che non sono utilizzati dal progetto e

che possono essere causa di problemi, catturando i

disturbi elettrici presenti attorno e nel circuito.

Up and Down

La tecnica più comune per evitare i problemi indicati ed attribuire al pin

un livello di tensione corretto è semplicemente quella di inserire un pull-up (o un pull-down), ovvero una resistenza tra il pin e la tensione

Vdd (o verso la Vss). Dunque:

| Pull-up |

resistenza tra l' ingresso e la Vdd |

| Pull-down |

resistenza tra l' ingresso e la Vss |

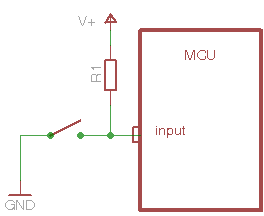

|

Con la resistenza di pull-up R1, il potenziale al pin di ingresso

non è più casuale, ma è determinato dalla Vcc. Alla chiusura dell' interruttore, il livello del pin sarà portato

a massa, ma con l' interruttore aperto Il livello è assicurato dalla resistenza. In una tabella:

| Interruttore |

Livello

input |

| Aperto |

Alto |

| Chiuso |

Basso |

|

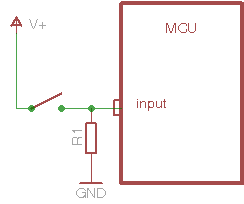

Possiamo anche, se necessario, invertire la logica.

|

Con la resistenza R1 collegata verso la massa (pull-down), il

potenziale al pin di ingresso con l'interruttore aperto è determinato

dalla Vss. Alla chiusura dell' interruttore, il livello del pin sarà portato

al livello alto, ma con l' interruttore aperto Il livello basso è assicurato dalla resistenza. In una tabella:

| Interruttore |

Livello

input |

| Aperto |

Basso |

| Chiuso |

Alto |

|

Ora, con le resistenze di pull-up o pull down abbiamo assicurato un

determinato e certo livello di tensione per entrambe le posizioni dell'

interruttore.

E il costo di una resistenza non influisce sul costo complessivo del progetto,

mentre elimina tutte le problematiche dei pin floating.

Quale valore per il pull-up ?

Ci si può porre il problema di quale valore scegliere per la R1 di pull-up

per l' ingresso di una porta logica.

In modo molto sintetico possiamo dire che il valore del pull-up

R1 deve essere in grado di portare a livello alto la tensione sul pin.

Questo dipende dalla corrente assorbita dal pin e dalla famiglia logica a cui

appartiene il dispositivo: da famiglia a famiglia i livelli accettati come

alto e basso variano.

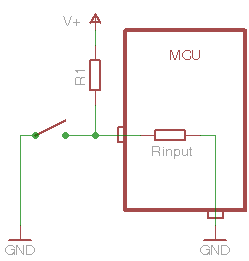

|

Va considerato che il circuito equivalente dell' ingresso può

essere sintetizzato come una resistenza.

Quando il contatto è chiuso, il pin è collegato direttamente alla

massa attraverso la bassa resistenza del contatto stesso e del suo

cablaggio, per cui il livello è sicuramente basso.

Quando l' interruttore è aperto, il livello di tensione al pin è

quello stabilito dal partitore composto da R1 e dalla resistenza dell'

ingresso Rinput.

O, in altre parole, la caduta di tensione su R1 determinata dalla

corrente che affluisce al pin dalla Vcc (attraverso R1) deve essere

tale da non scendere al di sotto del livello "alto" per quel

dato dispositivo. |

Vanno fatte due considerazioni:

- Quando il contato è chiuso, attraverso R1 passa una

corrente data da Vcc / R1. Se il valore di R1 è basso, la

corrente sarà elevata e questo non è di alcuna utilità al circuito,

anzi, è condizione che si cerca di evitare nelle realizzazioni che

richiedono un basso consumo

- Quando l' interruttore è aperto, il valore di R1 e della

corrente assorbita dal pin Iin determina la tensione al pin

stesso data da R1 * Iin, oppure alla tensione derivata dal

partitore R1- Rinput. Se R1 ha un valore troppo alto,

la tensione al pin non arriverà al livello alto

Quindi, la prima condizione tende a cercare valori di R1 il più alto

possibile, mentre la seconda tende ad abbassarne il valore.

La resistenza del pull-up può essere valutata approssimativamente con la

formula

RPU < [Vcc (min) - Vih

min] / Ii

dove Ii è la corrente di ingresso che il pin assorbe a livello

alto. I vari parametri si rilevano dal foglio dati del componente. Per quella

di pull-down il calcolo sarà relativo alla tensione VIL.

Però, dal punto di vista pratico, possiamo evitare ogni considerazione troppo

complessa (e che non è necessariamente funzionale) e possiamo dire che R1 dovrà avere un valore il

più elevato possibile, ma senza eccedere.

In pratica si può considerare la regola empirica, ma corretta,d i utilizzare

un pull-up pari a

1/10 della Rinput.

In queste condizioni siamo sicuri che la tensione

formata dal partitore R1-Rinput sarà sicuramente superiore a quella di

livello alto per qualsiasi famiglia logica.

- Per gate CMOS la resistenza di ingresso è dell' ordine di molte decine

di megaohm,

per cui la R1 potrà variare tra 100 kohm e 1 Mohm.

Va considerato che, anche se la resistenza del gate è di decine o centinaia

di megaohm, ci possono essere percorsi corrente non intenzionali, ad alta

resistenza, tra i pin dell' integrato, ad esempio a causa di sporco, residui

dei flussanti di saldatura, umidità e anche vie parassitarie all'interno l'IC

stesso. In generale questi percorsi sono dell'ordine di 10-100 mega ohm o più,

per cui, se si mantiene la resistenza di pull-up sotto il valore di 1 Mohm, la

scelta è adeguata.

Ovviamente valori molto minori, come il classico 10k andranno comunque

bene, anche se tenderanno ad avere un maggior consumo di corrente non

giustificato.

- Per ingressi di microcontroller, solitamente TTL compatibili, ma

realizzati con CMOS, la resistenza di

ingresso sarà dell' ordine del megaohm o più e quindi R1 potrà variare tra 10

kohm e 100 kohm.

- Per ingressi TTL la resistenza di ingresso è minore e anche R1 dovrà essere attorno a

5 kohm o meno.

In effetti, l' area anglofona distinguono:

- "strong pull-up" di

valore basso

- "weak pull-up" di valore elevato.

Per un

microcontroller si potrà considerare lo strong pull-up da 10 k e il weak pull-up 100 k

(circa).

Dato che 10 kohm è un valore comune, si può utilizzare questa resistenza per un pull-up di uso "universale",

anche se vanno fatte altre considerazioni.

- quanto più la resistenza ha valore basso, tanto maggiore sarà la

corrente assorbita quando il contatto è chiuso; quanto maggiore è la

resistenza, tanto minore sarà la corrente.

- per contro, nell pull-up, tanto maggiore sarà la resistenza, tanto più il livello

applicato al pin si avvicinerà al limite di theshold, dato

che maggiore sarà la caduta di tensione.

Questo vuol dire

che una tensione indotta dall' esterno non dovrà avere un valore

eccezionale per portare il pin nell' area di indeterminatezza.

Per contro,

un basso valore del pull-up porterà la tensione al pin più vicino alla

Vdd e quindi aumenterà la reiezione ai disturbi.

- Un'altra considerazione da fare è che maggiore è la resistenza di

pull-up, più lenta sarà una variazione di livello applicata al pin.

Questo è perché il circuito interno al pin, e sopratutto quello esterno,

hanno una capacità parassita che può anche essere significativa rispetto

alla frequenza dei segnali applicati quando è accoppiata con la resistenza di

pull-up.

Infatti si forma un filtro RC e questo necessita di tempo per cambiare di

stato. Se è richiesta una rapida variazione del segnale, un pull-up di

valore elevato, accoppiato con la capacità del pin e del circuito esterno

collegato, può limitare la velocità alla quale la logica cambia

stato in modo affidabile o, per lo meno, ridurre la velocità di

commutazione e deformare i fronti di salita e discesa del segnale.

Se

si conosce il valore del carico capacitivo, è possibile calcolare

la resistenza massima ammissibile di pull-up con alcune equazioni, ma va poi

verificato se il componente che pilota il pull-up può erogare la corrente

necessaria per portare il livello a "0"; se non è possibile,

occorre

utilizzare un valore più elevato di pull-up e ritrovarsi con un tempo di

salita maggiore sull'output oppure introdurre un buffer.

Tutti questi fattori vanno presi in considerazione.

Pull-up integrati & C

Se quanto detto a riguardo dei pull-up è estendibile anche ai pin

inutilizzati, va notato che, in alcuni casi, i costruttori raccomandano

proprio di lasciare

alcuni pin non collegati (nc - no connection). Le possibilità sono due:

- il pin non corrisponde ad alcuna connessione del silicio, quindi non ha

nessuna importanza il livello di tensione

- il pin ha funzioni riservate dal costruttore, ad esempio di test, e in tal

caso non va collegato ad alcun segnale esterno.

In ogni caso, dove il costruttore indica un nc è opportuno astenersi dal

collegare quel pin a qualsiasi cosa.

Ma esiste anche la possibilità che il costruttore abbia implementato

pull-up o, più facilmente, pull-down all' interno del chip per assicurare una

corretta polarizzazione a uno o più pin.

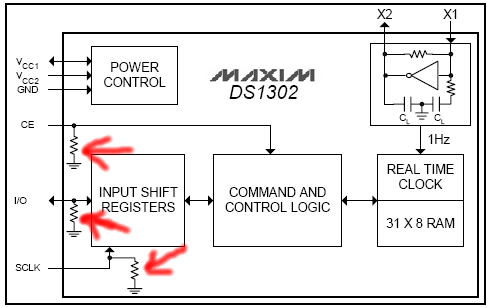

|

Ne è un esempio lo schema dell' RTC DS1302 di Maxim.

Possiamo osservare che il costruttore ha integrato resistenze di

pull-down sui pin di accesso seriale al chip, del valore di circa 40

kohm.

Questo serve a garantire un sicuro livello basso (i pin

sono attivi a

livello alto) nel caso di mancanza di connessione o di connessione con

bus ad alta impedenza.

|

In queste condizioni, è evidente che un pull-up esterno non ha molto

senso.

Pertanto, prima di prevedere sul circuito resistori di pull-up o pull-down

è esenziale consultare i fogli dati dei componenti, onde verificare la

struttura e le reali esigenza dei componenti.

Up e non solo

Quindi, se possiamo dire che resistori di pull-up sono utilizzati in circuiti elettronici per garantire che gli ingressi ai sistemi di logica

dei livelli definiti e certi, anche se i dispositivi esterni di ingresso

sono disconnessi o ad alta impedenza, dobbiamo anche ricordare che resistori

di pull-up sono utilizzati anche in altre situazioni.

Un pull-up può essere utilizzato all'interfaccia tra due diversi tipi

di dispositivi logici che operano a tensioni Vcc diverse.

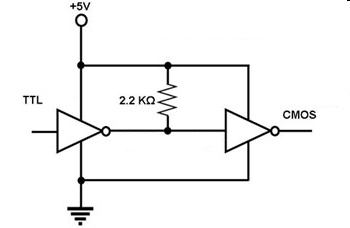

|

Ad esempio, nell' interfacciare l' uscita di una logica TTL con l'

ingresso di un CMOS, alimentati alla stessa tensione, un pull-up,

tipicamente tra 1 e 4.7 kohm dovrà essere inserito per assicurare il

giusto livello di tensione.

Ricordiamo che i livelli Vih e Vil per le due famiglie sono

differenti. Il pull-up garantisce che l' uscita a livello alto

raggiunga la Vih necessaria. |

|

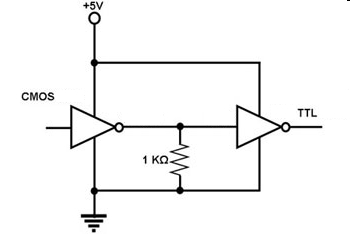

Analogamente, una interfaccia tra la tensione di uscita di un gate

CMOS e l' ingresso di una logica TTL, sempre alimentate alla stessa

tensione, sarà assicurata da un pull-down dell' ordine di 1 kohm. |

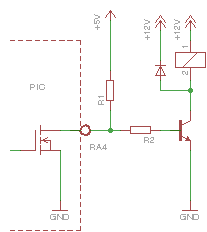

Ma un pull-up è anche il resistore che si applica all' uscita di un

dispositivo logico.

|

Un pull-up (o carico di collettore o drain) sarà richiesto per

interfacciare logiche con uscita open collector (oc) o open drain

(od).

La necessità di un pull-up di carico del collettore o del drain

non è presente solo in logiche TTL del genere 7406/7407, ma anche in

comparatori (LM339) o altri componenti lineari. Anche nei

microcontroller è possibile che alcune uscite siano open drain: ad

esempio il PORT RA4 nei PIC di Microchip e che richiede

quindi un pull-up per poter essere interfacciato con altri componenti.

|

In questo senso un pull-up costituisce anche il carico di un bus open

collector, ad esempio I2C o il PS/2 della tastiera/mouse del PC.

Resistori pull-up possono essere utilizzati su uscite logiche dove è

necessario ottenere tempi di commutazione spinti, iniettando più corrente nei

condensatori parassitari e riducendo il tempo dato dall' RC; in queste

condizioni spesso si preferisce a semplici pull-up dei terminatori

pull-up/pull-down, tipico il 220/330 ohm dei bus TTL, oppure terminatori

attivi (ad esempio nei bus SCSI).

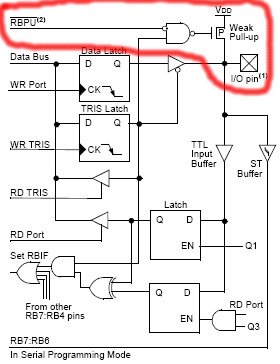

Weak Pull-up nei microcontroller

Alcuni port dei microcontroller dispongono di

weak

pull-up integrati, la cui inclusione è solitamente programmabile.

|

Nei PIC di Microchip solitamente i pin del PORTB hanno questa opzione.

Un bit RBPU permette di abilitare o disabilitare il pull-up.

I pull up integrati danno origine ad una corrente tra

50 e 400 microamps, con Vdd di 5V e il pin a massa.

Questo significa che il

valore resistivo dei pull-up integrati varia da 12.5 a 100 Kohms.

Questi weak pull up non sono resistori, ma vengono realizzati con MOSFET ad

elevata Rdon. La dispersione dei parametri costruttivi (la resistenza

varia con la Vds, il processo di fabbricazione e la temperatura) fa si che il loro

valore reale sia definito in un range abbastanza ampio.

I pull-up integrati sono previsti essenzialmente per evitare di avere resistenze all' esterno del

chip, dato che una applicazione embedded tende ad impiegare il minimo

possibile di componenti.

|

Queste "resistenze" integrate hanno lo scopo principale è di

fornire un percorso corrente per supportare contatti verso la massa,

come interruttori, tastiere, ecc. Nel caso di interfaccia con componenti

attivi vanno verificate le condizioni di lavoro e se necessario vanno

utilizzate resistenze di pull-up esterne.

Pull up vs. Pull down

Abbiamo parlato ampiamente dei pull up, ma non altrettanto dei pull down e questo ha alcune

ragioni, che ora cerchiamo di sintetizzare.

- Per quanto riguarda gli ingressi TTL va ricordato che occorre una

resistenza di valore minore per il pull down che per il pull up: gli

ingressi TTL che sono lasciati di sconnessi

intrinsecamente sono flottanti verso il livello alto, così da richiedere un

valore basso della resistenza di pull-down per forzare l' ingresso a 0.

In generale si può dare 5 k come valore di un pull up, ma 500 ohm come

valore di un pull down.

Quindi ne risulta che la corrente assorbita dal pull down diventa maggiore

di quella che scorre nel pull up e i progettisti solitamente hanno evitato

di ricorrere a questa soluzione, facendo del pull up la situazione di uso

comune.

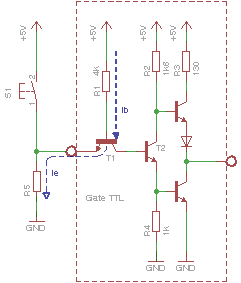

Per capire meglio il problema, osserviamo la struttura interna del gate

TTL, già visto all' inizio:

|

Consideriamo l' ingresso del gate TTL collegato al pull-up R5.

In linea di principio, potrebbe avere un valore abbastanza elevato

o essere anche assente, in quanto un ingresso TTL aperto fa scorre

una corrente Ib nella base del T1, limitata da R1. La corrente

entra nella base di T2 e l' uscita del gate è bassa.

Inserendo li pull-up, si conferma questa condizione, migliorando

il rapporto segnale/disturbo al pin di ingresso.

R1 potrebbe essere anche da 100 k, ma tuttavia si consigliano

valori nell' arco tra 5 e 10 kohm, per compensare le immancabili

tolleranze produttive del chip e i parametri di dispersione delle

connessioni esterne al pin. |

|

Supponiamo ora di collegare il contatto alla Vcc e quindi di

mandare a massa il pin di ingresso con un pull-down R5.

La corrente di base T1 scorre ora attraverso l' emettitore e la

R5 verso la massa e questo blocca T2 e l' uscita del agte è a

livello alto.

La corrente attraverso R5 produce una caduta di tensione e

questa non deve non deve superare 0,8 V per rientrare nei

parametri della Vil della famiglia TTL.

Con una corrente Ib di 1.1 mA, R5 non deve superare 720 ohm e si

consigliano valori nell' arco tra 390 e 500 ohm per compensare le

immancabili tolleranze produttive del chip e i parametri di

dispersione delle connessioni esterne al pin. Questo

è un immediato svantaggio in quanto la corrente in una R5 da 390

ohm, con il contatto chiuso, salirà a ben 13 mA, contro soli 500

uA nel pull-up da 10 kohm del caso precedente. |

- Se gli ingressi TTL aperti sono, in linea di principio, logicamente a

livello alto, diversa è la situazione dei circuiti CMOS.

Lo strato di ossido tra gate e source è teoricamente un perfetto isolante;

in pratica si standardizza una impedenza di ingresso di 1012

ohm. In questo caso non esiste una condizione di "default"

per il pin floating, ma occorre che sia imposto un livello preciso

attraverso un pull-up o un pull-down (ovviamente se il dispositivo

collegato all' ingresso non è di per sè in grado di fornire questi

livelli).

L' elevata impedenza sia nella

connessione a massa che in quella alla Vdd fa si che l' uso di pull up o pull down

sia solo una questione di stile, o meglio, di necessità della logica da

applicare.

Quindi, facendo riferimento alle tabelle presentate più sopra e di

seguito in

relazione all' ingresso di un contatto, la scelta up o down dipenderà

dalla comodità di una logica piuttosto che dell' altra.

Quanto detto non è proprio esattamente vero e anche nei CMOS il pull down

tenderà ad essere di valore inferiore al pull-up, il che, in circuiti a

basso consumo, può non essere la scelta migliore.

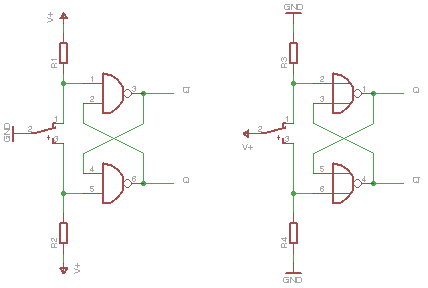

Per portare un esempio della funzione "logica" opposta di pull-up

e pul-down, niente di più evidente di un flip-flop RS

|

Nel flip-flop di sinistra è usata una logica NAND, in quello

destra una logica NOR.

La diversa risposta dei due tipi di gate ai livelli 1 e 0 porta

ad utilizzare pull-up per la prima soluzione (R1 e R2) e pull-down

per la seconda (R3 e R4).

Osservare che, in corrispondenza, lo switch che commuta il

flip-flop è collegato rispettivamente al GND o alla Vcc .

|

Ovviamente, in questo caso la scelta del pull-up o del pull down

dipende dall'obbligo di usare un tipo di gate piuttosto che un' altro,

dato che la risposta di questi è fissa.

Nel caso del microprocessore, utilizzare il contatto che chiude a

massa piuttosto che quello che chiude alla Vdd è del tutto

indifferente: come visto più sopra, la logica è invertita,

ma questo non presenta alcun problema in quanto essa non

dipende dall' ingresso, ma dalle istruzioni che la gestiscono !

Quindi basterà invertire anche il test del bit interessato

per individuare lo stato di apertura e di chiusura del contatto.

|

- Va anche ricordato anche che molti elementi, come opto isolatori,

comparatori, ecc, hanno uscita open collector (o open drain), il

che rende necessario un carico alla Vcc/Vdd, ovvero un pull-up. Il che

porta al più comune uso di questa soluzione.

- Inoltre si deve ricordare che, dove il pin di ingresso riceve segnali

che arrivano da distanze superiori a qualche decina di millimetri, ad

esempi da contatti esterni fuori dal circuito stampato e connessi con

cablaggi di decine di centimetri, si va in contro al rischio di captare

disturbi dall' ambiente. Un pull-up di basso valore forzerà in modo

maggiore lo stato del pin di ingresso verso una determinata tensione ed

aumenterà la tolleranza al rumore elettrico o elettrostatico (anche se,

nel caso in cui questo problema si presentasse, spesso occorrerà

intervenire anche con opportuni elementi addizionali, come filtri, opto

isolamento, ecc.).

- Last but not least, se colleghiamo il contatto alla Vcc/Vdd, questo vuol

dire che i conduttori che connettono il contatto steso al circuito sono

collegati alla tensione di alimentazione (uno ad interruttore aperto e

entrambi a interruttore chiuso). Siccome la massa (Vss/Gnd) costituisce la

parte rilevante del circuito con funzione spesso di schermo o collegate

alle parti metalliche per sicurezza, ne risulta che un contatto

accidentale tra i cavi dei contatti si risolve generalmente con un

cortocircuito tra la tensione di alimentazione e la massa, con le

evidenti conseguenze.

Nella connessione a pull up i contatti fanno riferimento alla massa

e la connessione con la tensione di alimentazione avrebbe in ogni caso una

limitazione di corrente dovuta alla resistenza del pull-up.

In sostanza, il progettista tende, anche se solo per

"tradizione", a utilizzare pull-up piuttosto che pull-down. Il che,

tutto sommato, è da considerare la scelta migliore.

In sostanza, però, tutti i metodi vanno bene: dipende dalle circostanze la

scelta di uno piuttosto che dell'altro e dalla necessità di minimizzare il

consumo oppure no.

Quello che deve essere compreso

è che il prodotto finale non deve avere

pin floating.

Nè, tanto meno, tratti di circuito stampato, spezzoni di cavo e simili

collegati a pin non utilizzati: tutto questo non farebbe altro che fornire una

antenna da cui captare ancor più facilmente ogni genere di disturbo

elettromagnetico ed elettrostatico !

In ogni caso, il montaggio deve essere ordinato, senza fili sparpagliati e

collegamenti volanti, senza mescolare connettori di uscita e di ingresso e

dotando il tutto di un un buon alimentatore.

Queste semplici norme , per lo più trascurate al di fuori dell' ambito

professionale, possono essere la soluzione di molti problemi di stabilità del

circuito.

|