|

LCD con caratteri a matrice

|

l

software di gestione: la lettura

Leggere

dal display

vuol dire accedere alla DDRAM, ma

anche al flag BF

ed all' AC.

Questo avviene sempre in relazione con i tre segnali di controllo:

- R/W che deve essere a livello 1

- RS che deve essere a 1 per dati e a 0 per il flag BF (assieme all' indirizzo

attivo in quel momento)

- E, che va portato a livello alto e poi di nuovo a livello basso una volta

letto il dato

Il diagramma, dal foglio dati di HD44780U, esemplifica il timing dei segnali in lettura:

Dal diagramma vediamo che sono evidenziati alcuni elementi sensibili; la

tabella riporta le temporizzazioni di HD44780U con alimentazione di

5 V e minore :

| Tempo |

Funzione |

Durata

[ns] |

Note |

| 5V |

<5V |

| tcyc |

Enable cycle time |

500

(min) |

1000

(min) |

Il ciclo di una operazione sul pin E non deve essere

minore di 0.5 us |

| tPW |

Enable pulse width, high |

230

(min) |

500

(min) |

La lunghezza dell' impulso su E non deve essere più

breve di 230 ns |

| ter / tef |

Enable rise/fall time |

20

(max) |

25

(max) |

Il fronte di salita e discesa dell' impulso su E deve

essere minore di 20-25 ns |

| tas |

Address setup time |

40

(min) |

60

(min) |

RS e RW devono essere validi prima dell' impulso su E |

| tah |

Address hold time |

10

(min) |

20

(min) |

RS e R/W devono essere stabili un tempo minimo

dopo la fine dell' impulso su E |

| tddr |

Data delay time |

160

(max) |

360

(max) |

Effettuando una lettura, il dato è valido dopo un certo

tempo dal

fronte di salita di E |

| tdh |

Data hold time, read |

5

(min) |

5

(min) |

Effettuando una lettura, il dato è ancora valido 5 ns dal fronte di

discesa di E |

Questi tempi sono quelli rilevabili dal foglio dati, ma va aggiunto che è

possibile trovare vari costruttori che dichiarano tempi leggermente

differenti, sopratutto se utilizzano controller compatibili con l' HD44780.

Anche per la lettura, possiamo osservare che il diagramma fissa alcune

temporizzazioni importanti.

In particolare :

- tddr : effettuando la lettura, il dato è valido al

massimo dopo 160

ns (360 ns) dal

fronte di salita di E

- tDH : questo indica che il dato va letto prima

rimuovere il livello alto di E

Qui tddr va controllato in funzione della frequenza del

clock del microcontroller: se la frequenza è molto elevata occorrerà una

attesa tra E a livello alto e la disponibilità dei dati sul bus.

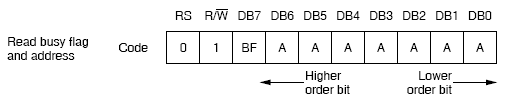

Mentre

in scrittura RS discrimina se si tratta di dati o comandi, in lettura ha

funzione di discriminare se si tratta del contenuto della RAM oppure del flag

BF.

|

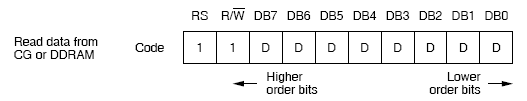

La

lettura dalla CGRAM o dalla DDRAM avviene in seguito alla scelta di una

delle due sezioni, all' indirizzo attivo in quel momento.

In entrambi i casi il dato letto è ampio 8 bit per cui, con l'

interfaccia a 4 bit occorreranno due letture successive per ottenere l'

intero byte. Nel caso di test di BF, anche se esso è il primo bit del

nibble alto (bit 7) occorrerà leggere anche il nibble basso, che, se

non utilizzato, potrà essere scartato..

|

|

L' acceso in lettura non dà origine alla necessità di

attese, dato che si sta leggendo un registro dl controller, che risponde in

tempi dell' ordine delle decine o centinaia di ns.

Possiamo però ignorare la lettura completamente se non interessano

azioni particolari sulla memoria del display.

Questo si ottiene collegando a massa il pin R/W e quindi bloccando il

controller in sola scrittura (RW=0); questo fa recuperare un pin di I/O sull'

interfaccia con il microcontroller.

Se la Vcc è minore di 5V

Come nel caso della scrittura:

Minore è

la tensione di alimentazione, maggiore è il dilatarsi dei tempi

necessari al controller per eseguire le funzioni richieste.

In generale, con alimentazione inferiore a 4.5 V (2.7-4.5 V) i

fogli dati danno tempi circa raddoppiati rispetto a quelli con

alimentazione a 5 V (4.5-5.5 V).

Si renderà necessario consultare il foglio dati del componente per

verificare i tempi critici con tensioni di alimentazione inferiori a

4.5 V. |

Non tutti i moduli sono uguali...

Come nel caso della scrittura:

va ricordato che molti moduli basati sulla

versione HD44780A riportano sul

foglio dati tempi di risposta più lenti di HD44780U:

| Tempo |

Funzione |

Durata

[ns] |

| 5V |

| tddr |

Data delay time |

360

(min) |

Chi intende utilizzare questi componenti, dovrà tenere presente queste

condizioni ed aggiungere sufficienti ritardi nel driver per ottenere le

giuste temporizzazioni.

Situazione analoga si verifica anche per moduli basati su altri

controller compatibili, tanto da poter trovare dei tempi indicati

sul foglio dati del controller e altri doppi indicati sul foglio dati

del modulo.

In ogni caso di dubbio, sarà opportuno consultare

il foglio dati.

In mancanza di questo, un

driver di sicurezza per il modulo dovrà considerare i tempi più lunghi,

salvo poi ridurli dove possibile.

|

|