Trasmissione dei dati

Su una linea seriale, i bit sono emessi come variazioni di tensione tra i due livelli logici 0 e

1, uno dopo l' altro.

Abbiamo detto che un a trasmissione asincrona non dispone di una

linea separata per il clock, come invece esiste in

SPI o I2C.

Come può, allora, il ricevitore riconoscere il bit trasmesso?

La chiave di comprensione della trasmissione asincrona è questa:

ogni impulso ha una durata ben precisa

che dipende

dal clock del trasmettitore e il tempo t di durata è pari a un periodo del clock

utilizzato.

Dunque, possiamo dire che, nella trasmissione asincrona (ASYNC) non esiste un clock separato

di riferimento, ma sono gli impulsi del segnale stesso ad avere attribuita una

durata ben determinata.

Questo rende il sistema molto

semplice ed economico, ma richiede, come vedremo subito sotto, che trasmettitore e ricevitore operino alla

stessa frequenza, la cui precisione

deve essere tale da impedire fenomeni di de sincronizzazione (frame error,

overrun error). Se trasmettitore e ricevitore utilizzano lo steso

identico valore di clock e il ricevitore ha un modo di sincronizzarsi con il

segnale del trasmettitore, ecco che il problema del clock separato è superato

e la comunicazione richiede almeno un conduttore in meno.

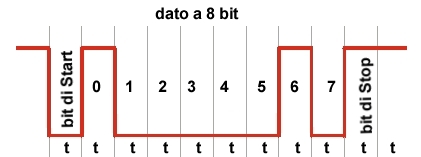

Per risolvere il problema della sincronizzazione, il tipico pacchetto dati

della RS-232 è composto da:

- un bit di start

- un byte dati

- un bit di stop

Questo vuol dire che, per ogni byte di dati trasmesso saranno

effettivamente emessi di 10 bit.

Così, la trasmissione del byte 01000001bin (41hex,

carattere ASCII 'A') corrisponderà al seguente grafico:

- La linea si trova normalmente nello stato di attesa o idle a livello alto

(1 logico).

-

La prima transizione da alto a basso indica l’inizio e prende il nome di

bit

di Start ed ha la durata di un tempo t. Questo bit iniziale ha lo

scopo di effettuare la sincronizzazione tra il clock del trasmettitore e

quello del ricevitore; questo si avvia in

corrispondenza del riconoscimento della prima transizione sulla linea dati.

- A questo fa subito seguito il

pacchetto dei dati, emessi a partire dal bit meno significativo (LSB), tutti

della stessa durata t, fino al bit più significativo (MSB). Da notare, quindi,

che il diagramma relativo ai dati va letto "al contrario", da destra

a sinistra, per ricostruire il valore del byte.

Questo non è per nulla problematico per i dispostivi di trasmissione e

ricezione, che fanno uso di registri di spostamento (shift register) e quindi

automatizzano il passaggio del dato da parallelo a seriale e viceversa.

- Il pacchetto è chiuso da un bit di Stop, la cui durata è analoga a quella

degli altri impulsi, ma che può essere prolungato, se necessario. Lo scopo di

questo bit è quello di completare la sincronizzazione tra trasmettitore e

ricevitore e finalizzare la chiusura del pacchetto trasmesso, a cui può

seguirne immediatamente un' altro, con la medesima

struttura.

Per quanto riguarda il tempo, ad esempio, con un clock di 4800 Hz, t sarà di

208,33 us e quindi la trasmissione sarà 208,33 x 10 = 2083,3 us. Se lo Stop, che può avere una lunghezza maggiore multipla

di t, ha la durata, ad esempio, di due bit, la trasmissione del pacchetto

richiederà 2291,63 us.

Questo se si considera la lunghezza del dato pari a 8 bit, che è un codice ASCII esteso.

Se si trasferisce un codice standard ASCII (da 0 a 127), 7 bit di dati sono

sufficienti, con un risparmio di tempo. Sono comunque possibili trasmissioni di dati con lunghezza diversa.

Così, anche se comunemente i messaggi comprendono caratteri ASCII o byte

esadecimali a 8 bit, molti moduli o componenti previsti per gestire la

comunicazione seriale (UART/USART) supportano anche comunicazioni con un diverso

numero di bit, nel range da 5 a 9.

Ad esempio, li codice baudot, tipico delle vecchie teletype,

utilizza 5 bit per rappresentare un carattere, mentre

è possibile realizzare sistemi "multi-drop", ovvero un

"bus" su cui sono connessi più dispositivi e in cui si impiega una

codifica a 9 bit per indicare se il dato trasmesso è l' indirizzo di una delle unità

collegate.

Ovviamente non esistono limiti per l' uso di altri codici, come il codice

Murray o EBCDIC o anche dati binari qualsiasi.

Va osservato che allo standard, che è relativo alla struttura della

trasmissione,

possono essere sovrapposti protocolli diversi, ad esempio includendo

nei messaggi dei pacchetti di checksum o altre tecniche di

sicurezza o organizzando i pacchetti di dati in modo particolare a

seconda delle esigenze della comunicazione.

|

In ogni caso, la lunghezza del pacchetto trasmesso è data da:

| numero bit dati + bit di Start + bit di Stop +

eventuale bit di parità |

dove il bit di parità è opzionale e lo Stop può avere una durata di 1t,

1/2t o 2t.

Quindi, un dato a 7 bit, senza parità, comporterà la trasmissione di

9 bit (7 dati + start + stop).

Se il dato è a 8 bit, con parità e con stop prolungato comporterà l'

emissione di 12 bit (8 dati + start + 2 bit di stop + bit di parità).

Ricezione dei dati

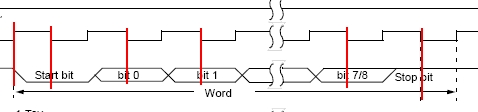

Una linea RS-232 è prevista a livello '1' in condizioni di riposo.

Questo fa

si che il bit di Start che avvia la comunicazione sia un impulso a livello '0'

della durata t.

Il

ricevitore rileva il fronte di discesa del segnale e, a partire da

questo, si predispone per la ricezione, avviando il proprio sistema di clock e i

contatori interni.

Sostanzialmente, a partire dal fronte di discesa del bit di Start, viene

attivata una attesa pari a 1/2 t, dopo di che il

ricevitore campiona lo stato della linea ad una cadenza

di tempo pari a t, il che fa cadere il campionamento al centro di ogni

impulso (dato che i due clock sono uguali).

Vari

dispositivi effettuano più di un campionamento per bit in modo da

neutralizzare eventuali disturbi sulla linea.

Inoltre, molto importante, il campionamento è effettuato per il numero di impulsi previsti dal

formato del pacchetto trasmesso e si

conclude con lo Stop, dove la linea ritorna a livello alto per almeno un tempo

t (1 Stop bit) o più. E' quindi evidente che trasmettitore e

ricevitore debbano essere impostati sia per la stessa frequenza che per lo stesso

formato del pacchetto.

In caso contrario il ricevitore effettuerà

campionamenti in punti errati, o per un numero diverso di passi, rendendo impossibile il riconoscimento del

dato.

A questo riguardo solitamente i dispositivi di ricezione sono in grado di

elaborare le situazioni di errore con alcuni segnali di errore:

- overrun error: la velocità di trasmissione ha un clock maggiore

da quello del ricevitore

- framing error: non viene rilevato correttamente il rapporto tra

il bit di Start e quello di Stop, ad esempio per una impostazione errata

della lunghezza del pacchetto o della frequenza dei clock

- parity error: se è impostata una parità, questa non risulta

rispettata

Sta al software di gestione del dispositivo attuare le misure necessarie in

questi casi.

E' evidente che il sistema asincrono, se ha il vantaggio di escludere la

necessità di una linea di clock separato, richiede che la frequenza di

trasmissione e quella del campionamento in ricezione siano per quanto

possibile identiche.

Il massimo errore ammissibile è quindi, teoricamente,

molto minore della durata di mezzo bit e va tenuto conto della possibile

deformazione dei fronti d'onda delle commutazioni dovuti alle

capacità/induttanze parassite del cavo di connessione e, per le trasmissioni

remote, dai problemi e disturbi di linea.

Pertanto il consiglio è di

utilizzare clock con una adeguata precisione e stabilità nel tempo e con le

variazioni della temperatura (1-2% o migliore), cosa che si ottiene

con oscillatori a quarzo.

Inoltre va tenuto presente che, quanto è maggiore

la frequenza di trasmissione, tanto minore sarà la durata degli impulsi e

quindi sarà critica la loro temporizzazione.

Da quanto detto, si evidenzia che:

- è impossibilità

di sospendere la trasmissione di un pacchetto di dati in una

trasmissione asincrona prima della

suo termine.

- Ed è pure impossibile prolungare un bit oltre il tempo t.

In queste circostanze il contenuto del pacchetto andrebbe perduto in quanto il

ricevitore continuerà a campionare il segnale in arrivo per il numero degli

impulsi previsti ed alla cadenza t, originando la ricezione di un dato errato.

Quindi, quanto permesso in trasmissioni sincrone (I2C, SPI), cioè uno

stretch del clock o al limite, anche la sospensione indeterminata della

trasmissione, non sono assolutamente possibili in RS232.

Ne deriva che l' uso di UART/USART (che si occupa autonomamente di

gestire i tempi) è la via più pratica per

implementare la comunicazione, mentre in un bit-banging (emulazione

software) si dovrà avere cura di rispettare con assoluta precisione i

tempi degli impulsi e impedire l' interruzione della trasmissione da

parte di altri processi.

|

|