Il protocollo I2C

Il protocollo ha le seguenti caratteristiche:

- Il trasferimento dati viene iniziato da un Master, con la linea di clock

come sincronismo. Come per SPI, si tratta di un sistema a shift register

ed essendo la linea clock separata da quella dati la sua frequenza può

cambiare durante la trasmissione senza danneggiarla.

- Inoltre è necessario che ogni dispositivo che trasmette sul bus

utilizzi un proprio clock. Data la natura sincrona della trasmissione, non

occorre una elevata precisione negli oscillatori, ma le periferiche

saranno più complesse che non semplici shift register.

- Non essendoci linee di selezione delle periferiche come in SPI, per la

comunicazione vengono utilizzati degli indirizzi a 7 o 10 bit. Anche

questo richiede una maggiore complessità delle periferiche.

- Contrariamente a SPI, sullo stesso bus possono essere presenti più

Master. Questo vuol dire che è necessaria una procedura di arbitraggio,

che è ottenuta manipolando le linee di clock e dati.

- La complessità è necessaria anche per supportare un sistema di

acnowledgement che consente ad ogni dispositivo Master di iniziare e

chiudere la trasmissione ed agli Slave di comunicare il successo o meno

del trasferimento dei dati. Questo è ottenuto manipolando le due linee di

collegamento.

Gli elementi fondamenti della trasmissione sono questi:

- la condizione di START (S)

- la condizione di STOP (P)

- la condizione di REPEATED START o RESTART (R)

- il pacchetto dati o indirizzo

- la condizione di ACNOWLEDGE (A)

Le "condizioni" sono i segnali che un dispositivo applica al bus

per comunicare lo stato corrente del bus e della trasmissione in corso.

Osserviamo in un diagramma una sequenza tipica di trasmissione:

La sequenza comprende:

- inizio trasmissione con la condizione di Start

- trasmissione indirizzo

- condizione di Acknowledge

- trasmissione dato

- condizione di Acknowedge

- trasmissione dato

- chiusura trasmissione con Not-Acknowledge e Stop

Osserviamo che, per un trasferimento di 8 bit, sono utilizzati 9 impulsi di

clock: questo impulso in più serve al protocollo per determinare la

condizione Acknowlege - Not Acknowledge.

Le condizioni del bus I2C

Sono chiamate "condizioni" delle particolari configurazioni delle

linee SDA e SCL che hanno lo scopo di comunicare ai dispositivi collegati al

bus lo stato della comunicazione in corso.

Vediamole in particolare.

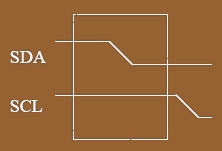

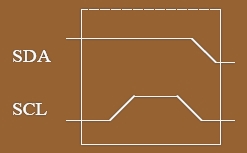

START

La prima condizione imposta è lo START: questa indica ai

dispositivi sul bus che uno di essi intende iniziare una trasmissione.

|

La condizione è realizzata mandando a livello basso la linea SDA

mentre la linea SCl è a livello alto, poi abbassando anche la linea

SCL.

Le temporizzazioni sono rilevabili dalle specifiche dei

dispositivi. Nel caso di impiego di microcontroller con moduli di

trasmissione sincrona, il problema di rispettare temporizzazioni

corrette è superato in quanto il modulo stesso provvede in tal senso,

a seconda del clock. |

La lettera S indica questa condizione.

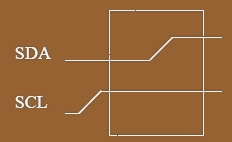

STOP

La condizione di Stop, indicata con la lettera P, segnala che il

dispositivo abbandona il controllo del bus.

|

Anche Stop è generato manipolando lo stato delle due linee: SCL

viene rilasciata e successivamente viene rilasciata anche SDA.

Alla fine della condizione di Stop, entrambe le linee sono a livello

alto grazie alle resistenze di pull-up (bus idle).

Una volta rilasciato il bus, esso può essere acquisito da un altro

dispositivo.

Anche in questo caso i moduli di comunicazione sincrona si fanno

carico delle corrette temporizzazioni. |

Start e Stop sono condizioni generate dal Master.

Il bus è considerato occupato dopo lo Start e libero un certo tempo dopo lo

Stop.

Le temporizzazioni sono specificate nella descrizione dello standard.

L' individuazione delle condizioni Start e Stop da parte dei dispositivi connessi al bus è facile se

essi incorporano l'hardware necessario. Nei microcontroller si tratta di un

modulo specifico per la gestione delle comunicazioni sincrone. Microcontroller senza tale interfaccia devono

testare lo stato della linea SDA almeno due volte più rapidamente della

frequenza del clock della trasmissione per rilevare correttamente la

variazione di stato della linea.

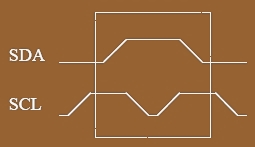

RESTART

La condizione di Restart (Repeated Start), indicata con R, segnala

che il dispositivo che sta controllando il bus intende inviare altri dati

senza rilasciare il bus stesso.

|

Questo è utile quando si sta comunicando con un dispositivo che

richiede un colloquio costituito da più bytes e che non è conveniente sospendere per evitare che un altro

dispositivo possa prendere il controllo del bus.

Sostanzialmente si tratta di una condizione di Stop seguita immediatamente

da una di Start, come possiamo vedere nel diagramma.

|

Una condizione di

Stop si ha quando SDA va alto mentre SCL è alto. Una condizione di Start si

ha è quando SDA è mandato basso mentre SCL è alto.

I moduli di gestione delle comunicazioni sincrone generare automaticamente

anche questa condizione con le corrette temporizzazioni.

Quando si utilizza una condizione di Restart invece di una condizione di

start?

Durante un trasferimento c'è spesso la necessità di inviare un comando e poi leggere

un dato di risposta dalla periferica. Questo richiede che il bus non sia preso

da un altro Master e l' operazione sia interrotta. Il protocollo definisce

quindi la condizione di Restart.

Normalmente, dopo avere inviato il byte dell'indirizzo (indirizzo e lettura/scrittura bit) il

Master può inviare un numero qualsiasi di byte, seguito da una condizione di

Stop. Però, se è necessario riallineare lo Slave prima di inviare altri

dati, invece di generare la condizione di stop è consentito inviare il

restart, seguito da un indirizzo.

Questa struttura ricorsiva consente un numero qualsiasi di condizioni di

restart per consentire operazioni di lettura/scrittura combinate su a uno o più dispositivi senza rilasciare il bus e, quindi, con la garanzia che l'operazione non

venga interrotta.

Un caso d'uso tipico è quello di accesso alle EEPROM. Occorre per prima

cosa selezionare il dispositivo inviando il suo indirizzo, seguito dal comando

di accesso; si inserirà ora un Restart per fare in modo che sia effettuata la

lettura all' indirizzo interno alla EEPROM voluto senza che un altro Master

prenda possesso del bus.

ACK e NACK

Un dispositivo può inviare una condizione ACK o riconosce un trasferimento di

un byte correttamente recepito portando basso la linea SDA durante il nono

impulso del clock.

Il protocollo I2C richiede che ogni byte trasmesso deve essere

concluso con un NACK o ACK.

|

8 impulsi del clock sono utilizzati per il sincronismo con i dati

trasmessi dal dispositivo master, mentre il nono serve a sincronizzare

la condizione di Acknowledge dell' unità ricevente.

Questo si ottiene mandando basso la linea dati. In caso contrario, SDA

sarà mantenuta a livello alto dal pull-up.

Quindi, per inviare un ACK occorre che la periferica agisca sullo

SDA. |

Siccome ACK è la conferma della corretta ricezione del dato, questa

condizione consente al master di verificare il fatto che la periferica

chiamata è connessa e attiva.

|

Infatti lo stato di NACK, ovvero la negazione della corretta

ricezione del dato è verificata dal livello alto di SDA sul nono

impulso di clock.

Siccome il bus non controllato (idle) è a livello alto per i

pull-up, NACK è una risposta "passiva": se la periferica

non risponde ACK al byte trasmesso, questo indica che o la

trasmissione non è andata a buon fine o la periferica non è attiva. |

Se occorre verificare la presenza di una periferica, sul microcontroller che governa il

bus

occorrerà implementare un sistema di per escludere o segnalare lo stato delle periferiche

che rispondono con un NACK.

La condizione NACK sarà presente quando:

- Nessun dispositivo di ricezione è presente all' indirizzo chiamato

- Il ricevitore è impossibilitato a ricevere o trasmettere

- Durante il trasferimento di dati il ricevitore ha ottenuto un dato o un

comando che non può comprendere

- Il ricevitore non può accettare ulteriori dati

- Un Master in ricezione segnala allo Slave che non intende ricevere

ulteriori dati

Al ricevimento della condizione NACK, il Master può generare la condizione

Stop per porre fine alla comunicazione, rilasciando il bus oppure un Restart per riavviare un

nuovo trasferimento dati, senza perdere il controllo del bus.

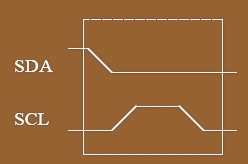

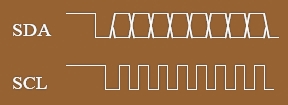

I DATI in I2C

I dati trasmessi sono a 8 bit, dato che lo shift register ha questa

dimensione. Se il dato ha dimensioni maggiori, occorrerà un adeguato numero

di trasferimenti a 8 bit.

|

Per ogni bit immesso sulla linea SDA viene generato un impulso di

clock sulla linea SCL.

I dati sono validi con SCL a livello alto. |

Quando SCL non è a livello alto, i dati possono cambiare. Byte di dati sono usati per trasferire tutti i tipi di

informazioni: quando si comunica con un altro dispositivo I2C, gli 8 bit di dati

possono essere un codice di controllo, un indirizzo o dati grezzi. Occorrerà

verificare i manuali dei vari dispositivi per individuare le specifiche

necessità: diverse periferiche potranno usare codici uguali con fini

differenti.

I dati devono essere validi al momento del fronte di salita del

clock.

I2C trasmette sempre per primo il bit più significativo (MSb).

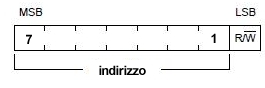

Gli INDIRIZZI sul bus I2C

Il primo byte che viene immesso sul bus dopo uno Start è quello di

indirizzo per la periferica da

attivare. I2C consente indirizzi a 7 bit o a 10 bit.

Nel primo caso, i bit dell' indirizzo occuperanno i 7 bit più significativi,

mentre il bit 0 (LSb) conterrà l' indicazione dell' operazione, se lettura o

scrittura.

|

Quando viene inviato, ogni dispositivo sul bus compara questo byte

con il proprio indirizzo e, se la comparazione ha successo, risponde

con un ACK. |

E' evidente che sullo stesso bus non possono coesistere due dispositivi con

lo stesso indirizzo.

Il bit 0 contiene l' informazione R/W che vale:

- 1 per indicare che è richiesta una lettura di dati

- 0 per indicare che sarà effettuata una scrittura di dati

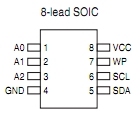

Dato che il fattore costo è sempre sensibile, è comune che vari

dispositivi abbiano un indirizzo fissato dal costruttore oppure limitato ad un

numero di possibilità molto ridotto, ad esempio 2; in altri casi il costruttore del dispositivo rende disponibili alcuni pin per

selezionare una parte dell' indirizzo.

|

Ad esempio, nelle memorie EEPROM, 3 pin del piccolo package a 8 pin

vengono dedicati alla selezione dell' indirizzo.

A lato la piedinatura di AT24CxxA di Atmel: i pin A2:0 vanno

polarizzati collegandoli a Vdd o Vss per formare parte dell'

indirizzo.

Nel caso di una AT24C01 o 02 (1K o 2K) tutti e tre i pin sono

attivi.

Però una AT24C16 (16k) non li utilizza, impiegando i bit forniti dal

Master nell' indirizzo per selezionare le pagine interne. |

La situazione non è comune, ma è possibile che si vogliano collegare più

periferiche uguali: ne risulta che, ove sia necessario avere sullo stesso bus

un numero di dispositivi superiore alla alla varietà degli indirizzi,

occorrerà spezzare il bus in segmenti, ad esempio con multiplexer (Philips

PC9544 o simili), gestiti separatamente. Per quanto I2C sia

strutturalmente flessibile, è chiaro che si tratta di un appesantimento.

Va osservato che l' assegnazione degli indirizzi ai dispositivi è

coordinata da uno specifico comitato (maggiori informazioni a www.nxp.com/i2c).

Esiste anche un documento Philips del 1997 i2c-bus

Allocation Table - General che riporta le assegnazioni di indirizzo di

vari dispositivi.

|